# I TU

# FAKULTÄT FÜR !NFORMATIK

# Robot4Web

Ein vom Anwender programmierbares, auf dem Internet basierendes Steuerungs- und Demonstrationssytem für Roboter

#### DIPLOMARBEIT

zur Erlangung des akademischen Grades

# Diplom-Ingenieur

im Rahmen des Studiums

#### Informatik

eingereicht von

#### Sandor Biro

Matrikelnummer 9327589

| an der<br>Fakultät für I                 | nformatik der 1   | Technischen | Universität Wien        |

|------------------------------------------|-------------------|-------------|-------------------------|

| Betreuung: Betreuer/Betre Mitwirkung: Di |                   |             | Dietmar Dietrich        |

| Wien, 28.10.2008                         | (Unterschrift Ve: | rfasser)    | (Unterschrift Betreuer) |

#### **Abstract**

The Project Robot4Web is dedicated for didactical and demonstrative purposes. The goal of this diploma thesis is to create a robot which is attached to a FPGA board and may be controlled by it. Additionally, a predefined application programmed into the FPGA may be used to control the robot directly via a serial interface. The robot movements and its environment may be observed via a Webcam which is also attached to the FPGA. This allows it to use the robot for research in the area of artificial intelligence.

The robot is connected to a PC via the programming cable of the FPGA and directly over a serial link. The complete development system for programming the FPGA and therefore the robot is realized in a Web application, allowing it to use the system in an e-learning setup.

#### **Kurzfassung**

Robot4Web ist ein Projekt, erstellt für didaktische und demonstrative Zwecke. Ziel dieser Diplomarbeit ist: einen Roboter herzustellen, der in erster Linie über ein FPGA-Board programmierbar und steuerbar ist. Darüber hinaus besteht die Möglichkeit, den Roboter mit Hilfe einer in FPGA programmierte Anwendung, über eine serielle Schnittstelle direkt anzusteuern. Sämtliche Bewegungen des Roboters, aber auch seine Umgebung werden mit einer Webkamera erfasst, die ebenfalls mit dem FPGA verbunden ist. Durch diese Tatsache wird ermöglicht, dass in weiterer Folge Forschungsarbeiten auf dem Gebiet der künstlichen Intelligenz durchgeführt werden können.

Die Anbindung des Roboters an den PC wird über ein FPGA-Programmierkabel und über ein RS-232-Kabel stattfinden. Die gesamte Entwicklungsumgebung für die FPGA-Programmierung, und dadurch für den Roboter, ist mit Hilfe einer Webanwendung realisiert worden. Damit wird die Einsetzbarkeit des Systems im Bereich des E-Learning ebenfalls ermöglicht.

### **Danksagung**

Ich möchte mich für das Verständnis, das mir meine Frau und mein Sohn entgegengebracht haben, mein Studium abschließen zu können, herzlich danken.

Ich möchte mich noch bei meinem Betreuer, Herrn DI Herbert Nachtnebel für die kompetente und immer bereite Unterstützung auch bedanken.

# Abkürzungen

**API** Application Programming Interface

**ASIC** Application Specific Integrated Circuit

**CLB** Configurable Logic Block

**CPLD** Complex Programmable Logic Device

**DCE** Data Communication Equipment

**DCI** Digitally Controlled Impedance

**DCM** Digital Clock Manager

**DCR** Bus Device Control Register Bus

**DTE** Data Terminal Equipment

**EDIF** Electronic Design Interchange Format

**FPGA** Field Programmable Gateway Array

**FSM** Finite State Machine

IC Integrated Circuit

**LUT** Look UP Table

**NCD** Native Circuit Description

**NFS** Network File System

**NGD** Native Generic Database

**NTFS** New Technology File System

**PCB** Printed Circuit Board

**PWM** Pulsweitenmodulation

**RTL** Register Transfer Layer

**SRAM** Static Random Access Memory

**UART** Universal Asynchronous Receiver / Transmitter

**UCF** User Constraints File

**UUT** Unit Under Test

**VHDL** Very High-Level Definition Language

**VPN** Virtual Private Network

# Inhaltsverzeichnis

| Kapitel 1  | Einführung                                   | 1  |

|------------|----------------------------------------------|----|

| 1.1        | Einsatz von Robotern und FPGAs in E-Learning | 3  |

| 1.2        | Abgrenzung                                   | 4  |

| 1.3        | Gliederung der Arbeit                        | 4  |

| Kapitel 2  | Von VHDL zum FPGA                            | 6  |

| 2.1        | FPGA Grundlagen                              | 6  |

| 2.2        | VHDL Grundlagen                              | 7  |

| 2.3        | Implementierung von VHDL-Code im FPGA        | 8  |

| Kapitel 3  | Die Steuerungshardware im FPGA               | 9  |

| 3.1        | FPGA Plattformen                             | 9  |

| 3.2        | Strukturelles Design                         | 10 |

| 3.2.1      | Einschränkungen im Modell                    | 10 |

| 3.2.2      | 2. Entity                                    | 11 |

| 3.2.3      | 3 Architektur                                | 13 |

| 3.2.4      | Das "User_Root" Modell                       | 15 |

| 3.2.5      | Signalgenerator Modell                       | 16 |

| 3.3        | Simulation                                   | 19 |

| 3.3.1      | Benchmarks                                   | 19 |

| 3.3.2      | 2. Simulationsablauf                         | 20 |

| 3.3.3      | B Ergebnisse der Simulation                  | 22 |

| 3.4        | Hardware Synthese                            | 22 |

| 3.4.1      | Syntheseablauf                               | 22 |

| 3.4.2      | 2. Eingabedaten                              | 23 |

| 3.4.3      | Syntheseergebnisse                           | 23 |

| 3.5        | Bitstrom erstellen und hochladen             | 23 |

| 3.5.1      | FPGA Pin-Zuweisung                           | 24 |

| 3.5.2      | Von der Logiksynthese zum Bitstrom           | 24 |

| 3.5.3      | Programmieren vom FPGA                       | 26 |

| 3.6        | FPGA Sicherheit                              | 26 |

| Kapitel 4  | Die Webschnittstelle                         | 28 |

| <b>4</b> 1 | Zugriffskontrolle und Anwenderverwaltung     | 28 |

| 4.2       | Streaming                                              | 29 |

|-----------|--------------------------------------------------------|----|

| 4.3       | Simulation und Synthese                                | 30 |

| 4.3.1     | Seitenaufbau                                           | 31 |

| 4.3.2     | Zwischenschritte für Simulation und Synthese           | 32 |

| 4.4       | R4W Seitemap                                           | 34 |

| Kapitel 5 | Der Roboter R4W                                        | 36 |

| 5.1       | Entwurf                                                | 37 |

| 5.1.1     | Arbeitsbereich und Freiheitsgrad                       | 37 |

| 5.1.2     | Auswahl der Motoren                                    | 38 |

| 5.2       | Pulsweitenmodulation                                   | 41 |

| 5.3       | R4W, Technische Daten                                  | 42 |

| 5.4       | Steuerung                                              | 44 |

| 5.4.1     | Explizite Steuerung                                    | 44 |

| 5.4.2     | Implizite Steuerung                                    | 47 |

| Kapitel 6 | Signalverstärkung und Schutz                           | 50 |

| 6.1       | Schutz                                                 | 50 |

| 6.1.1     | FPGA I/O Reflexionsschutz                              | 51 |

| 6.1.2     | Überspannschutz                                        | 51 |

| 6.1.3     | NOT-AUS Schalter                                       | 52 |

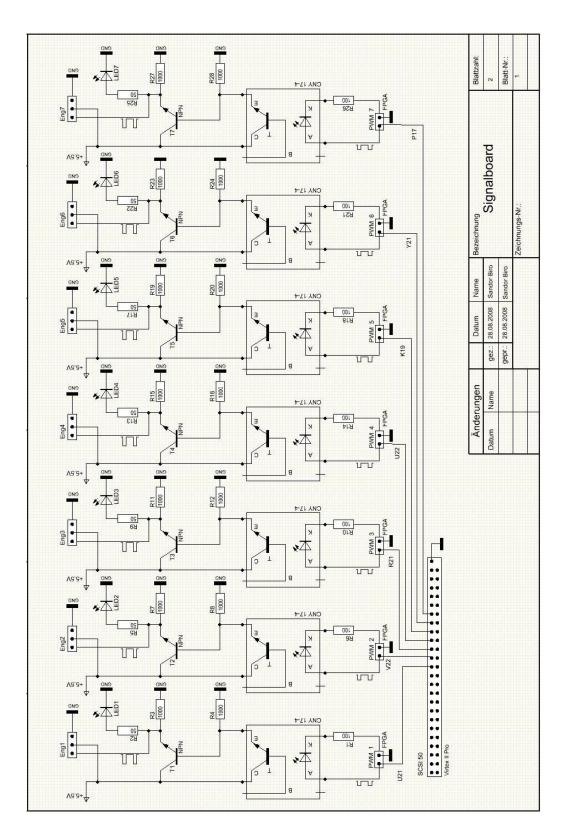

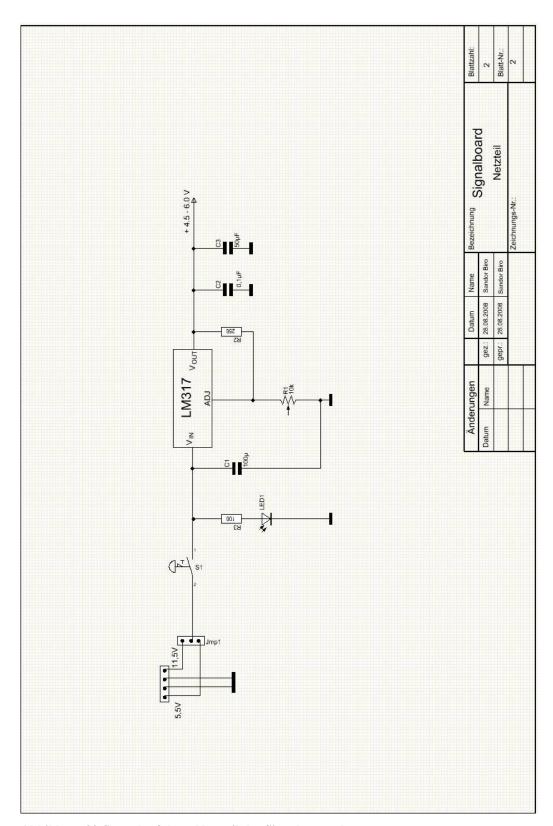

| 6.2       | Signalboard                                            | 52 |

| 6.2.1     | Aufbau des Signalverstärkers                           | 52 |

| 6.2.2     | Spannungsregler                                        | 55 |

| 6.2.3     | Anschlüsse                                             | 55 |

| 6.3       | Signalübertragung                                      | 57 |

| 6.3.1     | Optische Komponente                                    | 57 |

| 6.3.2     | TTL-Schaltung                                          | 58 |

| 6.3.3     | Mantelwellenfilter                                     | 59 |

| Kapitel 7 | Der Job Scheduler                                      | 60 |

| 7.1       | Aufgaben und Anforderungen                             | 60 |

| 7.1.1     | Ereignisse in den NTFS Dateisystem                     | 60 |

| 7.1.2     | ReadDirectoryChangesW API                              | 61 |

| 7.1.3     | Threadingmodelle                                       | 62 |

| 7.2       | Funktionsweise und Abläufe                             | 63 |

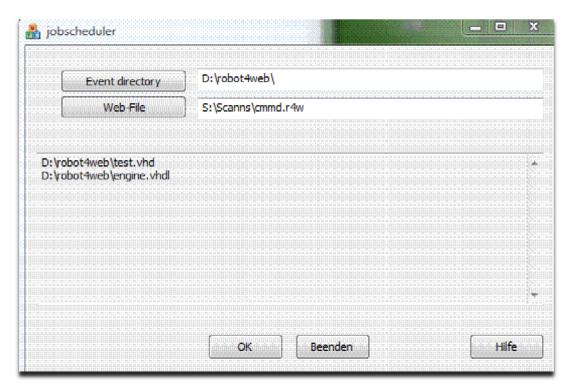

| 7.2.1     | Die grafische Oberfläche                               | 63 |

| 7.2.2     | Konfiguration                                          | 65 |

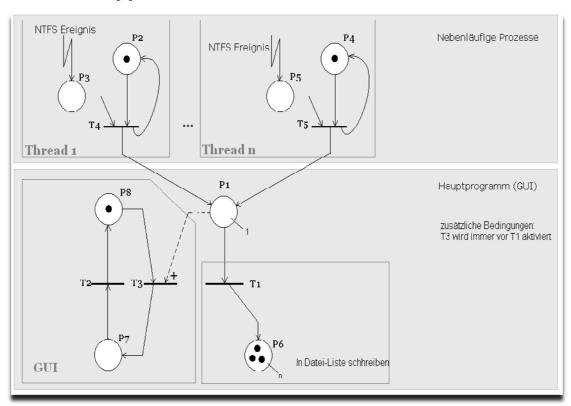

| 7.2.3     | Petri-Netz-Modell                                      | 66 |

| 7.2.4     | Realisierung                                           | 67 |

| 7.2.5     | Direkte Robotersteuerung über die RS-232 Schnittstelle | 69 |

| 7.2.6     | Aufgabensteuerung                                      | 72 |

| 7.2.7     | Job Scheduling über VPN                                | 73 |

| Kapitel 8 | Die RS-232 Schnittstelle                               | 74 |

| 8.1        | RS-232 auf dem Entwicklungsboard | 74 |

|------------|----------------------------------|----|

| 8.2        | Realisierung in der FPGA         | 75 |

| 8.2.       | 1 RS-232 Taktgenerator           | 76 |

| 8.2.       | 2 Serielle Signalübertragung     | 77 |

| Kapitel 9  | Schlussbetrachtung               | 79 |

| 9.1        | Zusammenfassung                  | 80 |

| 9.2        | Ausblick                         | 81 |

| Anhang     |                                  | 83 |

| Das Si     | gnalboard                        | 84 |

| uart.c     |                                  | 88 |

| RS232      | 2.cpp                            | 91 |

| CD im      | Anhang                           | 94 |

| Abbildun   | ngsverzeichnis                   | 95 |

| Tabellenv  | verzeichnis                      | 97 |

| Literatury | verzeichnis                      | 98 |

Das Internet ist heutzutage als eines der wichtigsten Kommunikationsmedien anzusehen, und die zur Verfügung stehende Bandbreite wächst stetig. Es existiert eine Reihe von Technologien zur Programmierung von Internetanwendungen und es werden vermehrt Systeme entwickelt, wo mit Hilfe von internetbasierten Technologien Teleoperatoren und Roboter angesteuert werden. Die Entwicklungsgeschichte der heutigen Industrieroboter führt bis zum Jahre 1940 zurück. Zunächst wurden Automaten entwickelt, die Sicherheit in nukleare Forschungslaboratorien verbessern sollten. Die späteren Weiterentwicklungen waren in der Lage, verschiedene, sich wiederholende Aufgaben durchzuführen. Die gegenwärtig produzierten Roboter sind mit besseren Sensoren und leistungsstarken Steuerungen ausgestattet, dadurch ist es möglich geworden, Roboter in der Medizin, im Halbleiterbau, Weltraumforschung und in anderen, mitunter höchste Präzision erforderlichen, Technologiebereichen einzusetzen.

Obwohl die Einsatzmöglichkeiten von Roboter kaum begrenzt sind, verwenden nur wenige Exemplare die Funktechnologie oder das Medium Internet für die Kommunikation mit einer externen Steuereinheit. Dies ist begründet durch einen großen Unterschied zwischen den Internettechnologien und modernen, eingebetteten Systemen, den sogenannten Embedded Systems. Während die eingebetteten Systeme in der Regel echtzeitfähig sind, fällt bei näherer Betrachtung der Internettechnologien auf, dass hier das Übertragungsprotokoll (TCP/IP, UDP, ...) und viele andere Komponente keine, oder nur eingeschränkte Echtzeitfähigkeiten besitzen.

Ziel dieser Diplomarbeit ist es, ein sechsachsiges Robotersystem für online Schulungen im Bereich FPGA (feldprogrammierbares Gatterarray), Design und Robotik zu entwerfen und zu realisieren. Das Robotersystem wird auf FPGA-Basis aufgebaut, und soll per Internet programmier-, sowie konfigurierbar sein.

Diese Plattform soll es Kursteilnehmern ermöglichen, Algorithmen sowie die Steuerungshardware des Roboters selbstständig zu Hause zu realisieren und mit Hilfe der vorbereiteten Entwicklungsumgebung zu prüfen. Für die Beschreibung der Steuerungshardware sollen Hardwarebeschreibungssprachen wie beispielsweise VHDL (Very High Speed Integrated Circuit Hardware Description Language) verwendet werden.

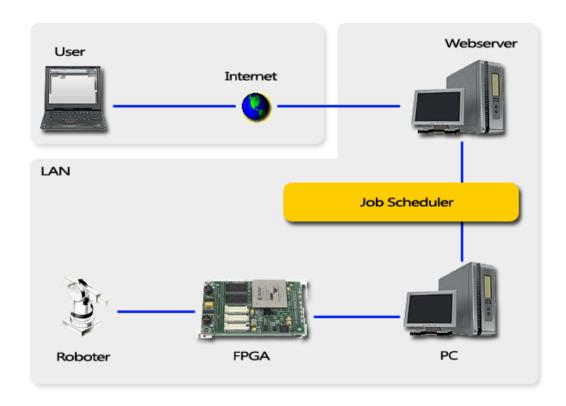

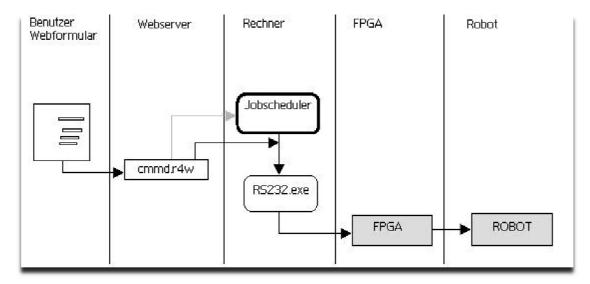

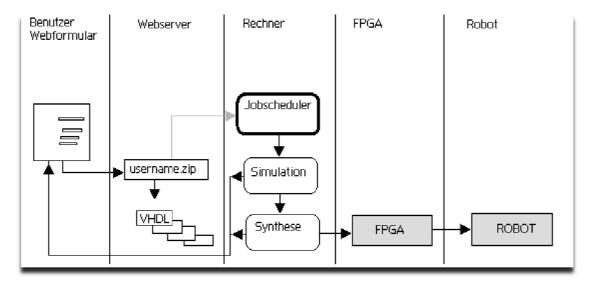

Das Robotersystem gliedert sich in die folgenden fünf, voneinander abhängigen, Komponenten: Den Webserver, den Job Scheduler, den Rechner für die Synthese und Simulation, das FPGA-Board und der Roboterarm.

Der bei diesem Projekt eingesetzte Webserver verwendet Microsofts Internet Information Services (IIS). Alle auf dem Webserver laufende Webanwendungen und Web Services werden mit ASP.NET in C# entwickelt. Die wichtigsten Aufgaben des Webservers im Robotersystem sind: Benutzerverwaltung, Darstellung des Prozesszustandes über das Internet, möglichst in "Echtzeit", und das Bereitstellen von Mechanismen, damit der Benutzer transparent auf externe Programme zugreifen kann.

Der Job Scheduler wird eingesetzt, um die Kommunikation zwischen dem Webserver und den PC's, auf denen die Simulation und die Synthese laufen, zu koordinieren. Der Job Scheduler löst die Steuerungs- und Verteilungsaufgaben des Systems, indem er auf die, durch externe Prozesse ausgelösten Ereignisse reagiert. Diese Ereignisse werden von ausgeführten Prozessen auf dem Webserver oder auf einem PC im Robotersystem erzeugt. Aufgaben des Job Schedulers sind: mehrere Client-PC's an einen Webserver zu binden, das Starten von ausführbaren Dateien gemäß der jeweiligen Benutzeranfragen durchzuführen, und die Rückgabewerte bzw. die Meldungen an den Webserver weiterzuleiten. Über eine grafische Oberfläche kann der Betreuer die Benutzerzugriffe kontrollieren, oder aber die Kontrollmechanismen gänzlich dem Job Scheduler überlassen.

Damit keine Fehler entstehen die die Systemintegrität bedrohen könnten, werden, bevor noch das Benutzerprogramm an das FPGA-Board weitergeleitet wird, umfangreiche Tests an diesem vorgenommen. Neben den Tests werden die Simulation und die Hardwaresynthese ausgeführt. Für diese Zwecke werden weitere PC's eingesetzt, die mit dem FPGA-Board direkt verbunden sind und den Job Scheduler ausführen. Diese PC's müssen Windows 2000, Windows XP oder Windows Vista als Betriebssystem verwenden, und im lokalen Netzwerk Zugriff auf den Webserver haben.

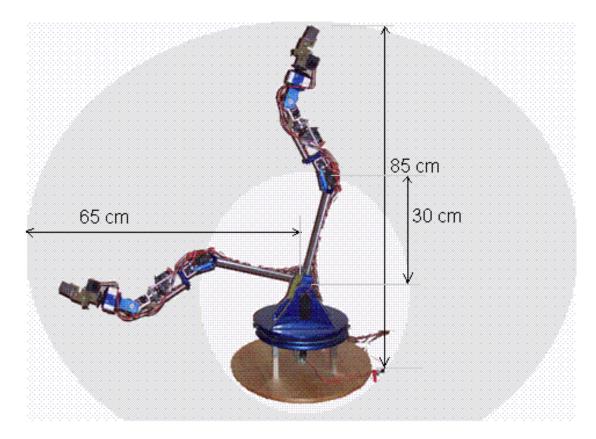

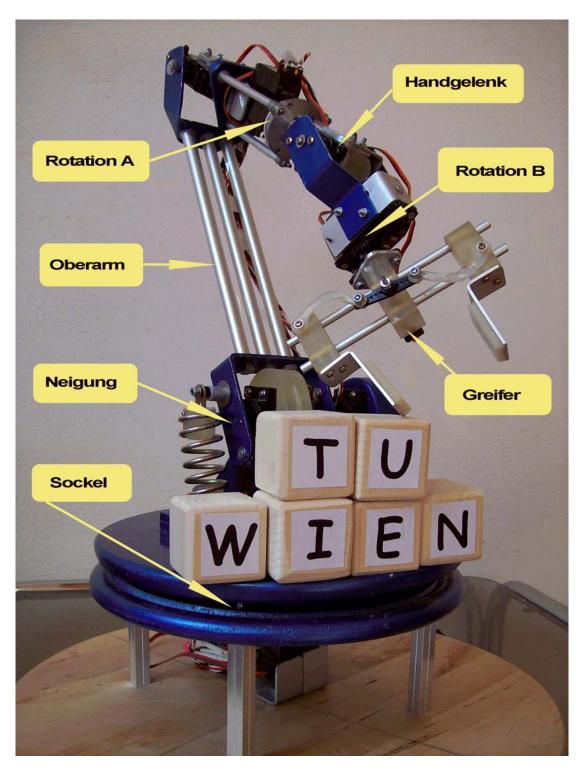

Der Roboterarm wird mit Hilfe von Servomotoren realisiert, da diese höheren Drehmomente liefern, und mit einer höheren Drehzahl betrieben werden können. Um die Steuerung des Roboters auch ohne direkten Sichtkontakt zu ermöglichen, werden Webcams in das System integriert, die ein Bild des Roboterarms am Bildschirm anzeigen. Die Daten dieser Webcams sollten gleichzeitig auch dem FPGA-Board übergeben werden, damit in weiterer Folge Forschungsarbeiten auf dem Gebiet der Bildererkennung durchgeführt werden können.

Um den Roboterarm anzusteuern, verwendet das Robotersystem ein Xilinx Virtex2 Pro Entwicklungsboard.

Abbildung 1: Die Robot4Web Topologie

# 1.1 Einsatz von Robotern und FPGAs in E-Learning

Roboter werden seit langem in der industriellen Produktion verwendet, und zwar meistens als Insellösung für spezielle Aufgabenbereiche. Durch die Weiterentwicklung der Internet- und Kommunikationstechnologien werden immer häufiger Roboter entwickelt, die universal einsetzbar sind; die nicht mehr vor Ort programmierbar sein müssen. Sie werden durch das Internet überwacht, und aus der Ferne programmiert. Neben dem industriellen Einsatz wurden Roboter und Robotersteuerungssysteme für das E-Learning entwickelt, um die Benutzung von teueren Hardware und Software möglichst leicht und effizient vermitteln zu können.

Das Technische Institut für Computertechnik auf der Technischen Universität Wien beschäftigt sich bereits seit längerer Zeit mit dem Design integrierter Schaltungen und deren Anwendung in E-Learning. Im Rahmen des Projekts "axis4web" können Studenten über einen einfachen Webbrowser von zu Hause aus ein Digitaldesign auf das - am ICT befindlichen - FPGA-Board uploaden, die Taster und Schalter des Boards betätigen, und den Zustand der 7-Segment-Anzeigen beobachten.

Eine weitere typische Anwendung von Roboter in E-Learning ist das "eLearning-Programm Lektor zur Handhabungstechnik". Lektor Handhabungstechnik ist für die berufliche Bildung in Schulen, Fachschulen, Fachhochschulen, bzw. in der Praxis konzipiert. Das Lernsoftware eignet sich besonders gut für die Ausbildung von Industriemechanikern und Mechatronikern, sowie für die Mitarbeiterschulung im Betrieb. Die einzelnen Module können zum selbstständigen Lernen in Einzelarbeit oder auch in Kleingruppen eingesetzt werden[23].

In dieser Diplomarbeit wird eine E-Learning Umgebung für die FPGA-Programmierung, und für die, mit dieser verbundenen Robotersteuerung geschaffen. Über diese Umgebung können zukünftige Studenten die in der Industrie etablierte Software für die FPGA-Programmierung kennenlernen und verwenden, und anschließend die Ergebnisse auf einen reellen Roboter umsetzen.

# 1.2 **Abgrenzung**

In dieser Diplomarbeit werden einige wichtige Aspekte der Robotersteuerung über das Internet wie Echtzeitigkeit, Zuverlässigkeit und Sicherheit nur marginal behandelt. Diese Bereiche betreffen nicht nur Hardware-Systeme, die online angesteuert werden, sondern alle zeitkritische Informationsübertragungen. Echtzeitfähigkeit, Zuverlässigkeit und Sicherheit sind die Grundlagen von neuen Internetgenerationen, und an der Weiterentwicklung der Methodik wird derzeit intensiv geforscht.

# 1.3 Gliederung der Arbeit

Obwohl "Robot4Web" die Steuerung eines Roboterarms über FPGA als Ziel hat, berühren Entwicklung und Implementierung mehrere Fachgebiete. Besonders die Entwicklung des Roboterarms erforderte viel Zeit, um dessen mechanischen Eigenschaften zu planen und die passenden Baumaterialien zu finden. So wurden beim Bau des Roboters Alu- und Kupferröhre, Holzteile, Alu-Profile, Epoxidharz, Schaum- und Kunststoff verwendet.

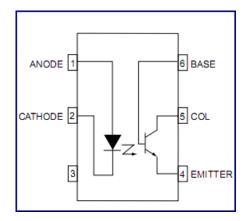

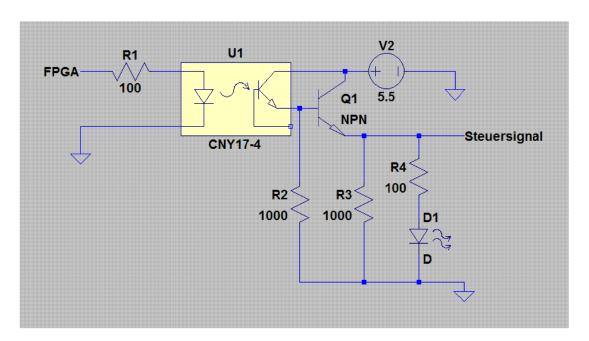

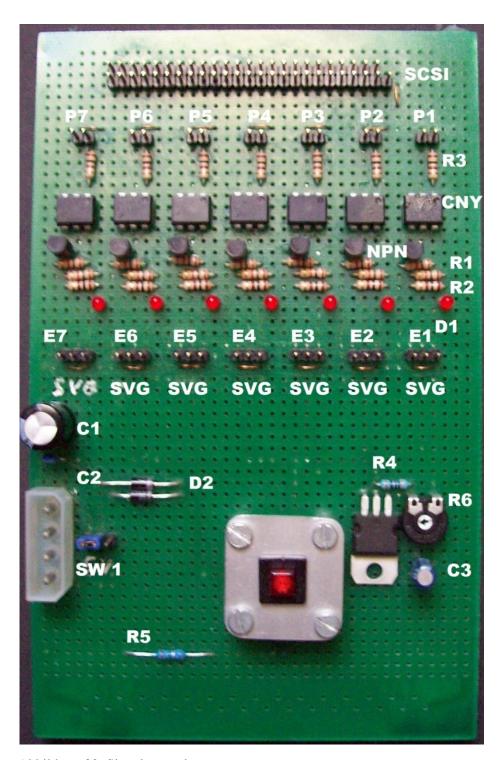

Für das als Schutz für FPGAs und als Signalverstärker gedachte Board wurde ebenfalls aus einzelnen Bauelementen gebaut. Bei der Erstellung des Signalboards wurden Optokoppler, PNP-Transistoren, Widerstände, Kondensatoren, Steckleisten, Schalter und weitere Bauelemente verwendet, die anschließend auf ein Board verlötet wurden.

Der Aufbau dieser Arbeit ist wie folgt gegliedert:

Kapitel 2 behandelt die Grundlagen von VHDL und FPGA, und stellt ein Zusammenhang zwischen Software- und Hardwareimplementierung.

Im Kapitel 3 werden die entwickelten VHDL - Modelle präsentiert. Anschließend werden die Simulation und die Synthese der vorgestellten Modelle besprochen, dabei wird der Ablauf dieser Vorgänge erläutert und die verwendete Software beschrieben.

Im Kapitel 4 wird die Webschnittstelle dargestellt. Diese lässt sich in folgenden Bereichen unterordnen: Anwenderverwaltung, Simulation und Synthese, Streaming und Webschnittstelle für die Robotersteuerung.

Kapitel 5 behandelt den Entwurf, die technische Spezifikation und die Steuerung des Roboterarms. Dabei werden die im Roboterbau eingesetzten Motorentypen besprochen, und miteinander verglichen. Anschließend werden die verschiedenen Robotersteuerungen gegenübergestellt und behandelt.

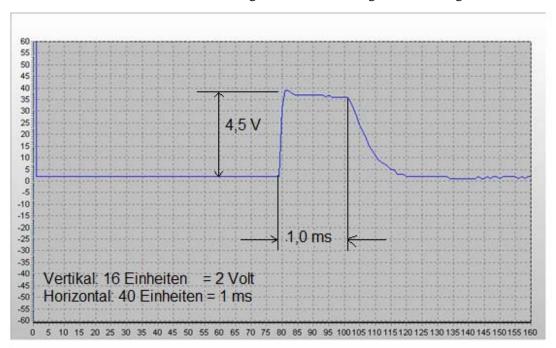

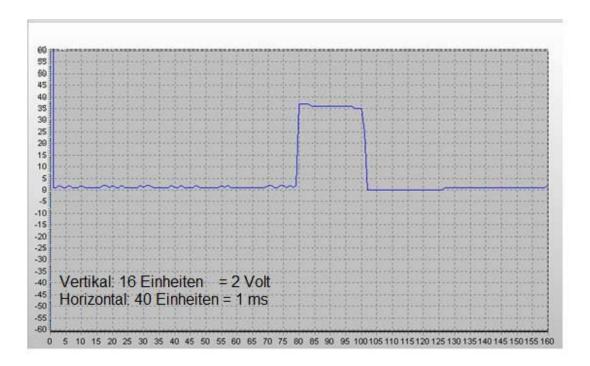

Im Kapitel 6 wird nach einer kurzen Einführung in Reflexion- und Überspannschutz, das Signalbord vorgestellt. Anschließend wird das übertragene Steuersignal analysiert und die Messergebnisse präsentiert.

Kapitel 7 ist dem Job Scheduler gewidmet. Hier wird das Programm, das für Robot4Web konzipiert und realisiert wurde, vorgestellt. Dabei werden die verwendete Kommunikationstechnik und die Einsatzmöglichkeiten ausführlich beschrieben.

Kapitel 8 beschreibt die UART-Kommunikation. Speziell wird die Realisierung auf ein FPGA näher behandelt.

Eine Zusammenfassung der Arbeit wird im Kapitel 9 gegeben, ein Ausblick auf weitere Forschungsaspekte und zukünftige Anwendungsgebiete sind im Unterkapitel "Ausblick" besprochen.

Im Anhang (Kapitel 10) sind dokumentierte Abbildungen und entwickelte Programmcodes untergebracht. Auf diese Elemente wird in den vorangegangenen Kapiteln Bezug genommen.

Kapitel 2 Von VHDL zum FPGA

# Kapitel 2 Von VHDL zum FPGA

In diesem Kapitel werden im Abschnitt 2.1 die Grundlagen und die verwendete Technologien der FPGA Boards beschrieben, auf denen Robot4Web aufbaut. Im Abschnitt 2.2 wird die Entstehungsgeschichte von VHDL kurz zusammengefasst dargestellt, und letztendlich wird im Abschnitt 2.3 die Implementierung von VHDL Code im FPGA beschrieben.

# 2.1 **FPGA Grundlagen**

Der Begriff FPGA wird in dieser Diplomarbeit noch häufig verwendet, und bedarf eine kurze Zusammenfassung.

Die englische Abkürzung FPGA steht für Field Programmable Gateway Array und ist ein Programmierbarer Integrierter Schaltkreis.

Die Industrie hat durch ihre Entwicklung immer kompliziertere Steuerungen und Regelungseinheiten benötigt. An dieser Stelle hatte Ron Cline die Idee, einen beliebig konfigurierbaren Baustein zu realisieren, der dann von Ingenieuren vielseitig eingesetzt werden kann. So sind die SPLA, Simple Programmable Arrays entstanden. Mit den ersten programmierbaren Schaltkreisen hat man nur logische Schaltungen realisieren können.

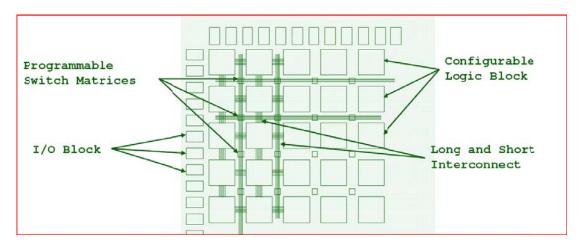

Die erste FPGA-Architektur ist 1985 vom Herrn Freeman - ein Xilinx Mitbegründer - entwickelt worden. FPGA's unterscheidet sich von SPLA dadurch, dass anstelle einfacher logischer Gatter logische Blöcke (CLB) verwendet werden. Diese logischen Einheiten werden bei der Realisierung von komplexen logischen Funktionen eingesetzt. Eine wichtige Komponente der logischen Blöcke ist die Look-Up-Table (LUT). Abhängig von der Anzahl der LUT Eingänge, kann man alle binäre Funktionen mit n Variablen realisieren, wobei n die Anzahl der LUT-Eingänge ist. Die Abbildung 2 zeigt das vereinfachte FPGA Modell mit den konfigurierbaren logischen Blöcken. Die I/O Blöcke ermöglichen die Kommunikation zwischen den im FPGA-Schaltkreis angelegten dichten Verbindungskanälen und der Peripherie. Der Aufbau der logischen Einheiten in der FPGA erlaubt die Implementierung von sequenziellen und kombinatorischen Automaten.

Kapitel 2 Von VHDL zum FPGA

Abbildung 2: Vereinfachtes FPGA Modell

# 2.2 VHDL Grundlagen

Zielsetzung der VHDL Beschreibungssprache ist die Beschreibung von Verhalten und Funktion digitaler Schaltkreise. Weiterhin sollte ein vom Hersteller und Technologie unabhängiger, weltweiter Standard zur Beschreibung digitaler Hardware geschaffen werden. Mit Hilfe dieser Technologie ist das Planen, Simulieren und Synthetisieren von digitalen Schaltkreisen möglich geworden. Obwohl die VHDL Sprache sehr umfangreich ist, ist es trotzdem nicht möglich, alle in VHDL geschriebenen Codestücke in ein beliebiges FPGA zu implementieren. Die Implementierung wird durch die Synthetisierungssoftware, durch FPGA Eigenschaften oder einfach durch die gewünschte Geschwindigkeit, mit der die Applikation laufen soll, begrenzt.

Bereits in den 70-er Jahren ist die Notwendigkeit von Simulation und Synthese von Schaltkreisen erkannt worden. In den 80-er Jahren erscheinen die ersten VLSI (Very Large Scale Integration) integrierte Schaltkreise. Die integrierten Schaltungen beinhalten immer mehr Komponente (ROM, Register, etc.), Planung und Entwurf von neuen Schaltungen kommt mit der klassischen Methode nicht mehr aus. Alternative Wege werden gesucht.

VHDL erscheint im Jahre 1981, wird aber erst 1987 zum ersten Mal genormt und wird im weiteren etwa alle fünf Jahre überarbeitet. Beispielsweise ist 1993 der IEEE 1076 Standard überarbeitet und neu genormt worden.

Neben VHDL existieren noch andere Hardwarebeschreibungssprachen wie Verilog oder SystemC. Wegen der einfachen und leicht verständlichen Syntax von VHDL und wegen seiner weitreichenden Möglichkeiten, ist VHDL besonders im didaktischen Bereich sehr verbreitet. Eine Erweiterung von VHDL auf analoge Systeme ist mit VHDL-AMS definiert worden (VHDL analog / mixed signal).

Kapitel 2 Von VHDL zum FPGA

# 2.3 Implementierung von VHDL-Code im FPGA

Der Planungsablauf von dem VHDL-Code bis zu einem in FPGA implementierbaren Schaltkreis beinhaltet drei Schritte: Spezifikation, Simulation und Synthese. Bei der Realisierung und in der Praxis werden diese Stritte noch weiter unterteilt und können einmal, oder auch zyklisch ausgeführt werden.

Spezifikation und System Design sind die ersten Schritte im VHDL Design Flow. Welche Aufgaben der geplante Schaltkreis zu lösen hat, wird gleich während der ersten Schritte bestimmt. Am Ende dieses Schrittes erhält man einen Schaltkreisentwurf, den man entweder aus logischen Bauelementen, ROMs und Registern realisieren kann, oder einfach mit Hilfe von VHDL beschreibt. Wenn man den Schaltkreis durch VHDL beschreibt, dann erhält man den zu implementierenden Schaltkreis nach der Hardwaresynthese. Der generelle Aufbau einer VHDL-Spezifikation beinhaltet die Schnittstellen-Beschreibung, Architektur eines Bausteins und Konfiguration.

Die Simulation dient grundsätzlich zur Verifizierung des funktionellen Verhaltens eines Designs. Es ist wichtig zu wissen, dass der einwandfrei simulierbare VHDL - Code nicht unbedingt in einem bestimmten FPGA implementierbar sein muss. Für die Simulation und Verifizierung von VHDL Code werden Softwaresimulatoren wie beispielsweise ModelSim von Mentor Graphics eingesetzt.

Zielsetzung der Hardwaresynthese ist die möglichst schnelle und kostengünstige Synthese elektronischer Hardware in einen FPGA zu realisieren. Die Hardwaresynthese wird von speziellen Synthesewerkzeugen erledigt, die meistens herstellerspezifisch sind. In diesem Schritt wird ein mit VHDL modelliertes Modell mit Hilfe einer Herstellerbibliothek in die FPGA befindlichen logischen Einheiten implementiert. Während der Hardwaresynthese werden die logischen Gatter zusammengeschaltet, die I/O Ports bestimmt und zu den Eingängen und Ausgängen des Schaltkreises geordnet. Letztendlich wird der so erstellte Code in den FPGA geladen. Grundsätzlich sind diese Schritte nicht mehr Plattformunabhängig, viele Faktoren können die Implementierung beeinträchtigen, wie die Anzahl der I/O-Böcke oder die verwendete Herstellungstechnologie. Die meisten plattformabhängigen Einstellungen werden von den verwendeten Syntheseprogrammen, basierend auf die Herstellerbibliothek, erledigt.

Für die erfolgreiche Realisierung von implementierbaren VHDL - Modellen ist die Beachtung des inneren Aufbaus der zugrunde liegenden FPGA absolut notwendig.

# Kapitel 3 **Die Steuerungs**hardware im FPGA

Für diese Diplomarbeit wurden zwei VHDL - Modelle entwickelt, um die Robotersteuerung zu demonstrieren, und als Plattform für zukünftige Applikationen zu dienen. In diesem Kapitel werden für Robotersteuerung entwickelte VHDL - Modelle vorgestellt und erläutert. Anschließend wird die Simulation und Synthese der vorgestellten Modelle und die verwendeten Entwicklungswerkzeuge beschrieben. Zum Schluss werden die Automatisierung und die Anbindung dieser Vorgänge über die Webinterface beschrieben.

### 3.1 **FPGA Plattformen**

Als Zielplattform für die Realisierung von digitalen Schaltungen wurde die Xilinx FPGA-Familie gewählt. Alle für dieses Projekt erstellten VHDL-Modelle sind auf Xilinx Virtex II-PRO und Xilinx Spartan 3A FPGAs getestet und implementiert worden.

Als Plattform für die verwendeten FPGAs dienen von unterschiedlichen Herstellern entwickelte Entwicklungsboards. Auf den Entwicklungsboards sind I/O-Anschlüsse, Konfigurationsspeicher, Erweiterungssockel, RAMs, AD/DA Wandler und weitere Erweiterungen angebracht. Die angebrachten Erweiterungen dienen der Speicherung von Konfigurationen, der Umwandlung physikalischer Größen, der Taktgenerierung oder sind mit den entsprechenden Kontrollern ausgestattete Schnittstellen.

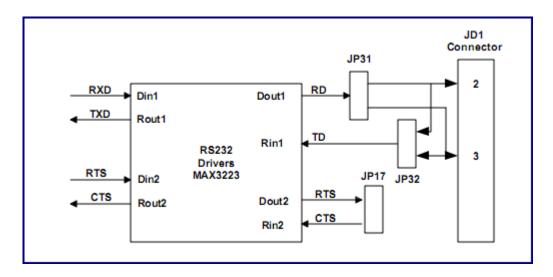

Für den Xilinx Virtex-II Pro FPGA 2VP7-FG456 dient ein von der Firma Memec hergestellte Entwicklungsboard als Plattform. Der Spartan 3A FPGA ist auf einem einfacheren Entwicklungsboard von Digilent angebracht. Beide Plattformen besitzen für das Projekt Robot4Web wichtige I/O-Anschlüsse, unter anderem die seriellen Schnittstellen. Die verwendeten seriellen Schnittstellen und die Implementierung von synthetisierten UARTs wird in einem späteren Kapitel noch ausführlich beschrieben.

Zur Synthese und zum Konfigurieren beider FPGAs wird das windowsbasierte Project Navigator ISE 9.2 von Xilinx verwendet. Das Hochladen von Bitströmen geschieht über Programmierkabeln. Um die Virtex II-Pro FPGA zu konfigurieren, wird das Xilinx

Programmier- und Debuginterface Parallel Cable IV über die JTAG-Schnittstelle verwendet. Die Konfiguration von Spartan 3A FPGA gestaltet sich einfacher, da hier ein handelsübliches USB-Kabel verwendet wird.

Mit Hilfe von Jumpern, die sich auf den Entwicklungsboards befinden, können diese in verschiedene Programmiermodus versetzt werden. Es gibt insgesamt vier Programmiermodi: Boundary Scan Mode, Master-Serial Mode, Slave-Serial Mode und Select Map Mode, die abhängig vom Hardware Support der Boards unterschiedliche Konfigurationsgeschwindigkeiten aufweisen. Während der Entwicklung wird der Boundary Scan Modus bevorzugt.

# 3.2 Strukturelles Design

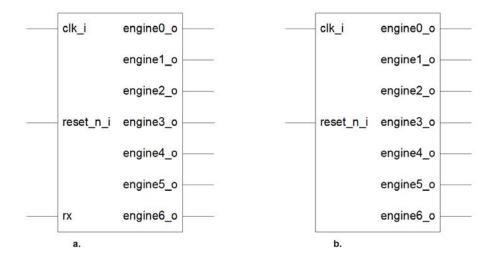

Um die Steuerung des Roboterarms über die bereitgestellte Webinterface zu ermöglichen, wurden zwei VHDL Modelle für die implizite und explizite Steuerung erstellt. Beide VHDL Modelle verwenden die gleiche Top-Level-Struktur, mit dem Unterschied, dass bei der expliziten Steuerung ein zusätzliches Signal für die UART Übertragung ("rx") gebraucht wird.

### 3.2.1 Einschränkungen im Modell

Da die Zielsetzung ein System ist, das von den Anwendern programmierbar ist, wurde das VHDL Modell so konzipiert, dass nur ein Teil der Module von den Anwendern veränderbar ist. Diese Einschränkung ist notwendig, da durch fehlerhafte Programmierung oder falsche Konfiguration Schäden entstehen können in der Anlage selbst, oder in der Umgebung.

Aus oben erwähnten Sicherheitsgründen, um die Systemintegrität zu bewahren, wird es den Anwendern nicht erlaubt, die Grundeinstellungen für die FPGA-Entwicklungsboards zu verändern. Diese Grundeinstellungen betreffen die Pin-Belegungen, und Takt- und Reset-Einstellungen des Entwicklungsboards.

Durch die Zuweisung von falschen Pin-Belegungen kann man den verwendeten FPGA stark beschädigen, oder sogar unbrauchbar machen. Die geringfügige Veränderung der Grundfrequenz in der Konfiguration hat eine große Auswirkung auf die Stellgeschwindigkeit und auf die Positionierung der Servomotoren. Eine gröbere Veränderung der Grundfrequenz von dem bestehenden Modell bewirkt, dass die generierten Steuersignale nicht mehr für die Servosteuerung geeignet sind. Ein Beispiel: bei Verwendung von 25MHz anstelle von 50MHz als Grundfrequenz in der FPGA werden die Pulsweitenmodulierte Steuersignale 2 bis 3 ms Lang sein. Die Servomotoren können aber Steuersignale nur im Bereich von 1ms bis 2ms Länge interpretieren.

Eine weitere Auswirkung der veränderten Grundfrequenz ist, dass die übertragene UART Signale von dem Baudgenerator erstellten Abtastsignale nicht richtig abgetastet werden. Die so entstandenen Steuersignale erzeugen dann unvorhersehbare Bewegungen des Roboterarms, da die gestellten Anforderungen nicht mehr erfüllt werden.

Das Top-Level Modell des, für die Robotersteuerung erstellten VHDL Modells, bildet der Plattform für die zukünftige Applikationen. Wegen der getroffenen Einschränkungen ist das Top-Level Modell von den Anwendern nicht veränderbar. Durch den modularen Aufbau von logischen Schaltungen in VHDL ist es leicht, die Schaltung so anzuordnen, dass die als empfindlich angesehene Komponente in einem Modul zusammengefasst wird. Um den Anwendern die Möglichkeit zu bieten, ihre logischen Schaltungen zu erstellen und in diese Umgebung zu integrieren, wurde das Modul "main\_modul" vorgesehen.

### **3.2.2** Entity

Auf der oberen Ebene (Top Level) werden Eingang- und Ausgangssignale des gesamten zu simulierenden Systems beschrieben. Auf der nachfolgenden Abbildung ist die äußere Sichtweise, eine Abstraktion von der eigentlichen physikalischen Schaltung, der Top-Level Modell von der expliziten und impliziten Steuerung dargestellt.

Die verwendeten TOP-Level Modelle haben zwei bzw. drei Signaleingänge und insgesamt sieben Signalausgänge. Diese Signale werden in der "TOP.UCF" –Datei spezifiziert und den entsprechenden FPGA Pins zugewiesen.

Das Signal "clk\_i" ist die Takt Signalquelle mit 50MHz Taktfrequenz, und hat eine Periodendauer von 20ns. Per Definition ist das Taktsignal ein Rechtecksignal mit 50% HIGH und 50% LOW Anteil. Das "clk\_i" Signal wird zu jedem einzelnen Teilmodul zugeführt und ermöglicht, dass die einzelnen Module synchron arbeiten bzw. Schaltvorgänge und Zustandswechsel ausgelöst werden.

Das Signal "reset\_n\_i" ist ebenfalls ein Eingangssignal. Er wird verwendet, um die gesamte Hardware-Logik asynchron in einen definierten Ausgangszustand zurückzusetzen. Entsprechend der Konfiguration, kann der Reset Signal HIGH oder LOW Initialwerte erhalten. In unserer "TOP.UCF" –Datei wird "reset\_n\_i" mit dem Zustand HIGH initialisiert.

Das "rx" Signal wird für die serielle Datenübertragung verwendet. Die gesendeten Signale werden mit 9600 Baud übertragen. Bei jeder erfolgreichen Signalübertragung werden 8 Bits seriell übertragen. Da ein ganzer Befehlssatz aus 24 Bits besteht, werden die generierten Steuerbefehle in drei Schritte übertragen.

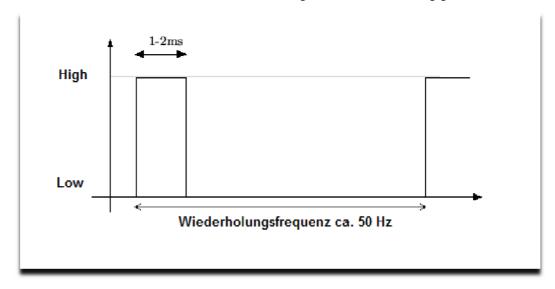

Aus der Abbildung 3 ist zu entnehmen, dass das verwendete Modell sieben Ausgangssignale hat. Durch die Ausgangssignale "engineX\_o" - wobei X die Nummer des korrespondierenden Robotergelenks ist - werden die Servomotoren gesteuert. Das Steuersignal ist ein Rechtecksignal, mit einer Periodendauer von 20 ms und eine Impulsdauer von 1 bis 2 ms Länge. Diese Signale werden von dem Signalgenerator-Modul erzeugt. Bei Signalgenerator-Modul handelt es sich um einen Modul, der wegen den getroffenen Einschränkungen durch die Anwender nicht veränderbar ist.

Abbildung 3: Top-Level Modell. a.) explizite Steuerung. b.) implizite Steuerung

Die äußere Sichtweise spiegelt sich in der Entity Deklaration wieder. Im nachfolgenden Codeausschnitt ist der Top Entity beschrieben. Alle hier beschriebenen Signalleitungen werden in der "TOP.UCF" –Datei zu den I/O-Schnittstellen dem zu Grunde liegenden FPGA zugewiesen.

Neben jedem Ausgangssignal sind die anzusteuernden Robotergelenke als Kommentar dazugefügt.

```

entity top is

port (

-- Eingangssignale

: in std logic; -- 50MHz Taktsignal

: in std_logic; -- UART

reset n i : in std logic; -- asynchron Reset

-- Ausgangssignale

engineO o : out std logic; --Steuersignal, Sockel

engine1 o : out std logic; --Steuersignal, Neigung

engine2 o : out std logic; --Steuersignal, Oberarm

engine3_o : out std_logic; --Steuersignal, Rotation A

engine4_o : out std_logic; --Steuersignal, Handgelenk

engine5 o : out std logic; --Steuersignal, Rotation B

engine6 o : out std logic --Steuersignal, Greifer

);

end top;

```

Listing 1: Top Entity des R4W Modells.

#### 3.2.3 Architektur

Die Beschreibung der Funktionalität eines Moduls wird in der Architektur(Architecture Body) zusammengefasst. Dies kann auf vielfältige Weise geschehen. Die VHDL Beschreibungssprache erlaubt die Programmierung einer Verhaltensbeschreibung, die Verwendung von Strukturbeschreibungen oder beides miteinander kombiniert.

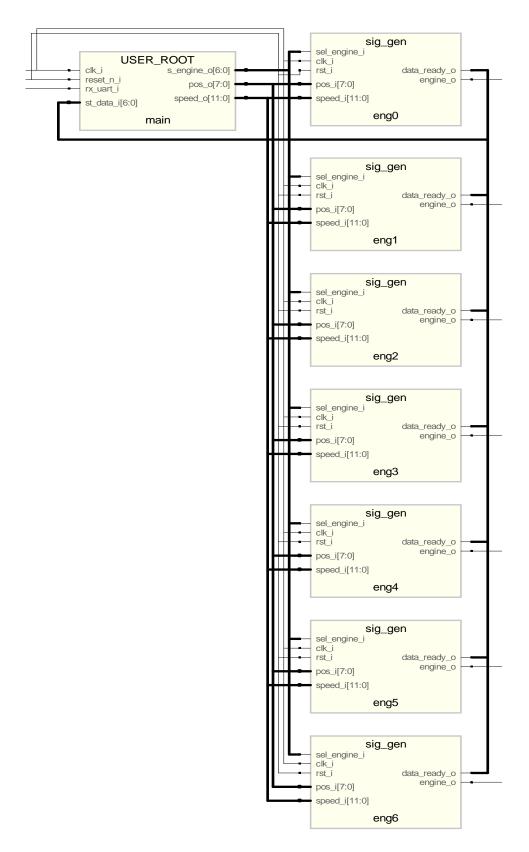

Auf Abbildung 4 ist der strukturelle Aufbau des Top-Level Modells dargestellt. Aus dem Modell ist es einfach zu entnehmen, dass die Architektur des Top-Level Modells auf zwei grundlegende Modelle aufgebaut ist. Aus den verwendeten Modulen werden Instanzen gebildet, die dann durch deklarierte Signale miteinander verdrahtet werden. Auf dieser Ebene ist keine weitere Verhaltensbeschreibung notwendig. Die weiteren Hierarchieebenen bestehen jedoch vollständig oder nur teilweise aus Verhaltensbeschreibung.

Unter Berücksichtigung der getroffenen Einschränkungen wurde das gesamte VHDL Entwurf so konzipiert, dass alle Komponente, die von Anwendern erstellt wurden, in einem Modul zusammengefasst werden können. Dadurch wird erstens die Sicherheit erhöht, und zweitens die Übersichtlichkeit und Handhabung wesentlich erleichtert.

Um das Anwendermodul von dem Rest der Top-Level Architektur Komponenten leichter zu trennen, wurde für die Top-Level Architektur die Strukturbeschreibung gewählt.

Abbildung 4: Innere Sicht des Top-Level Modells.

#### 3.2.4 Das "User\_Root" Modell

Die VHDL-Entity des Modells ist vorgegeben, deswegen müssen alle Eingangs- und Ausgangssignale im Anwendermodul definiert sein. Die Architektur vom "User\_Root"Modell kann vom Anwender selbst gestaltet werden, dabei können weitere Module oder das Verhalten beschrieben werden.

In die Entity des "User\_Root" Modells sind die Eingangssignale "clk\_i" und "reset\_n\_i" unverändert von dem Top-Level Modell übernommen. Diese Signale steuern die globale Taktung und das asynchrone Zurücksetzen. Das "rx\_uart\_i" Signal wird für die serielle Datenübertragung verwendet. Es besteht nur aus einer Signalleitung, und wird ebenfalls von der Top-Level Entity unverändert übernommen, ohne Verwendung lokaler Signale.

Von dem Signalgenerator Modul wird der Erhalt neuer Befehle mit einem Signal quittiert. Von allen sieben Signalgeneratoren werden die Signalleitungen in einem Signalbus zusammengefasst, und an das User\_Root Modul weitergeleitet. Die Busbreite des "st\_data\_i" Signalbuses entspricht der Anzahl der Signalgeneratoren, und somit der Anzahl der Robotergelenke. Um die Signale von dem Signalgenerator zu dem User\_Root Modul zu verdrahten, werden in der Top-Level Architektur lokale Signalleitungen verwendet. Der Anwender hat in seinem Programm sicherzustellen, dass Signale nur dann übertragen werden dürfen, wenn von allen Instanzen des Signalgenerators die Bereitschaft des Datenempfangs signalisiert wurde.

Ausgangsseitig wird der "User\_Root" Modul mit dem Signalgenerator direkt verdrahtet. Über die Signalbusse "s\_engine\_o", "pos\_o" und "speed\_o" werden die Signalgeneratoren ausgewählt, die neuen Positionen und die gewünschte relative Geschwindigkeit angegeben.

Das Signalbus "s\_engine\_o" besteht aus sieben Signalleitungen, für jede Instanz des Signalgenerators eine Signalleitung. Mehrere Instanzen des Signalgenerators können durch gleichzeitige Setzung von Bits auf dem "s\_engine\_o" Bus ausgewählt werden, und so die berechnete Kommandos simultan zu übertragen. Dieses Verhalten ist sehr nützlich, wenn der Roboterarm in einen sicheren Zustand gebracht werden soll, oder bei Aktivierung des Reset-Knopfes der Ausgangszustand angefahren werden soll.

Die Positionierung des Robotergelenks wird mit einer Auflösung von 8 Bit angesteuert. Das heißt, dass ca. 200 Grad (die maximale Verstellwinkel des Servomotors) in 256 Schritte aufgeteilt wird. Ein Schritt entspricht weniger als ein Grad Verstellwinkel und nähert sich der Grenze, die die verwendeten analogen Servomotoren erreichen können. Die Wert zur Berechnung der relativen Geschwindigkeit wird über das Signalbus "speed\_o", mit einer Busbreite von 12 Bit an den Signalgenerator gesendet.

#### Anwendungsbeispiel

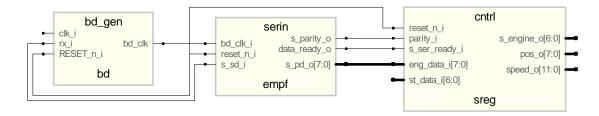

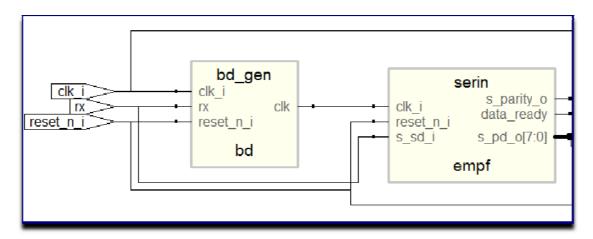

Auf Abbildung 5 ist der strukturelle Aufbau des "User-Root" Moduls dargestellt, wie es in der expliziten Steuerung eingesetzt wird. Da bei der seriellen Übertragung eine genaue Ab-

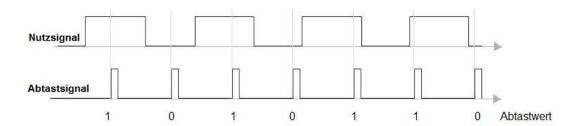

tastung der empfangenen Signale zusätzlich noch zu realisieren ist, wird ein Baudgenerator erstellt. Der Baudgenerator erstellt ein Taktsignal, das mit dem vereinbarten Übertragungstakt übereinstimmt. Bei einer Übertragungsrate von 9600 Baud ist die erstellte Abtastfrequenz 2604-mal kleiner, als die globale Taktfrequenz von 50MHz.

Die seriell gesendeten Signale sind weiterhin auf ihre Integrität zu prüfen. Die Überprüfung und die Zusammenfassung der Signalbits werden im "serin" Modul behandelt, bevor die als parallele Signale an die "cntrl" Module gesendet werden.

Abbildung 5: Innere Struktur des "User Root" Moduls für die serielle Steuerung.

Wegen der getroffenen Einschränkungen muss die Möglichkeit gegeben sein, das "User\_Root" Modul separat zu den vorhandenen Modulen zu laden. Dazu ist es notwendig, die Simulation- und Synthese-Ablauf so zu gestalten, dass dieses Modul zu den bestehenden Grundkomponenten dazugeladen und integriert wird. Das Laden von Anwendermodule wird vom Webinterface und vom Job Scheduler im "Hintergrund" erledigt.

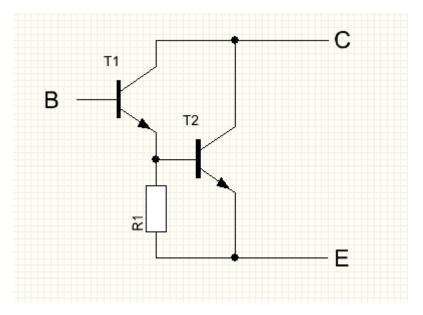

#### 3.2.5 Signalgenerator Modell

Der Signalgenerator ist eines der grundlegenden Module, und bildet den wichtigsten Teil des VHDL Modells. Der Anwender hat keinen Zugriff auf dieses Modul, wodurch dies nicht verändert werden kann. Der Signalgenerator hat die Aufgabe, ein kontinuierliches Steuersignal, basierend auf den Eingangsparametern zu erstellen. Das generierte Steuersignal ist ein pulsweitenmoduliertes Signal mit einer Wiederholfrequenz von 50 Hz.

Das "User\_Root" Modell bildet mit jeder Instanz des Signalgenerators und mit den dazugehörigen Signalleitungen bzw. Signalbusse einen geschlossenen Regelkreis. Wodurch insgesamt sieben in sich geschlossene Regelkreise entstehen.

Die Ausgangsgrößen des Regelkreises sind die sieben Steuersignale, die Rückführung wird durch die Signalleitungen "st\_data\_i" gebildet, der Regler selbst ist das "User\_Root" Modul, wobei die Signalgeneratorinstanzen als Prozesse angesehen werden. Die Führungsgrößen im Regelkreis sind in der Top-Level Entity definierte Eingangssignale.

Der Signalgenerator wird in der Top\_Level Architektur instanziiert und verdrahtet. Vom "User\_Root" Modell wird über die Signalleitungen "s\_engine\_o" jeder Instanz signalisiert, dass neue Eingangsdaten angelegt wurden. Die angelegten Signale müssen mindestens eine

Periode lang(20 ns) unverändert an den Signaleingängen des Signalgenerators liegen, um diese von jeder Signalgeneratorinstanz richtig interpretiert werden zu können.

Weitere Eingangssignalen sind "pos\_i" und "speed\_i". Beide Signale entsprechen den Ausgangssignalen vom "User\_Root" Modul, wo diese ausführlich auch beschrieben wurden. Durch die Möglichkeit, dass jeder Signalgeneratorinstanz Eingangsdaten zugewiesen werden können, und sie gezielt aktiviert werden können, erreicht man, dass jede Instanz voneinander unabhängig, verschiedene Steuersignale generieren kann. Die generierten Steuersignale werden über die "engine\_o" Signalleitungen ausgegeben, dann verstärkt an die Steuerleitung der Servomotoren angelegt.

#### Steuersignale erstellen

Im Gegensatz zu Schrittmotoren, sind die Servomotoren nicht darauf ausgelegt, mit unterschiedlicher Stellgeschwindigkeit angesteuert werden können. Es ist gelungen, das Zeitverhalten dieser Elektromotoren mit den generierten Steuersignalen so zu manipulieren, dass die Stellgeschwindigkeit und sogar die Beschleunigung der Servomotoren mit 8 Bit Auflösung zu regeln ist.

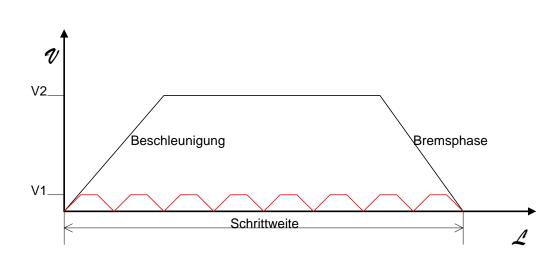

Da nur die gewünschte Sollposition angegeben werden kann, ist die Ansteuerung von Servomotoren viel einfacher als bei der Schrittmotoren. Aus der erhaltenen Sollposition und aus der aktuellen Position berechnen die Servo-Regler die Anfahrtsbeschleunigung und die Bremsphase. Je größer die Entfernung zwischen aktueller Position und Zielposition, desto höher ist die erreichte Geschwindigkeit nach der Beschleunigungsphase. Wenn man die Endposition nicht in einem Schritt sondern in vielen kleineren Schritten zurücklegt, dann sind die erreichten Geschwindigkeiten nach jeder Beschleunigung weitaus kleiner als bei einem Schritt.

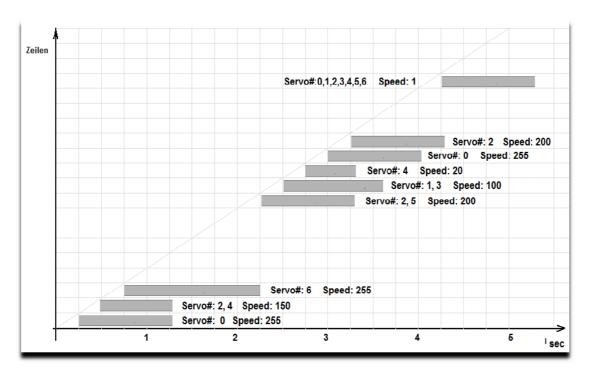

Abbildung 6: Servomotor Anfahrtsgeschwindigkeiten in Abhängigkeit der gewählten Schrittweiten.

Auf Abbildung 6 sind die erreichten Geschwindigkeiten in der Abhängigkeit der gewählten Schrittweiten dargestellt. Es ist leicht zu nachvollziehen, dass die gewählte Schrittweite die Anfahrtsgeschwindigkeit beeinflusst.

Auf Abbildung 6 der rot dargestellte Bewegungsablauf führt zu einer ruckartigen Bewegung des Roboterarms, da jeder Schritt auf der Darstellung erst nachdem der Servoarm zum Stillstand gekommen ist, gestartet wurde.

Um die Beschleunigung und die Bremsphase aus dem Bewegungsablauf zu eliminieren, müssen die Steuersignale so verschoben sein, dass bei gleich bleibender Schrittweite die Geschwindigkeiten konstant bleiben. Das wird dadurch erreicht, dass die Position der nachfolgenden Schritte bereits vor dem Eintritt in die Bremsphase versendet wird. Auf Abbildung 7 wird durch dicke Linie die tatsächliche Bewegung dargestellt. Die dünnen Linien zeigen den theoretischen Anfang jedes Schrittes. Tatsächlich sind die dünnen Geraden fast vertikal, da der Servomotor die maximale Anfahrtsgeschwindigkeit bei der gegebenen Schrittweite bereits erreicht hat.

Abbildung 7: Sukzessive Erhöhung der Anfangsgeschwindigkeit von Servomotoren

Die Anfahrtsgeschwindigkeit lässt sich zweierlei regeln. Durch die Erhöhung der Schrittweite und durch die Änderung von den Abständen, in dem die neue Position gesendet wird, verändert sich auch die Geschwindigkeit, mit der von der Startposition in die Zielposition gelangt wird.

Die Berechnung der Geschwindigkeiten und Schrittweiten ist die Aufgabe vom Signalgenerator Modul. Um die aktuelle Position des Robotergelenks im VHDL Modul zu kennen, wird dieser Wert im Signalgenerator ständig aus den vorangegangenen Zielpositionen und aus internen Zuständen immer neu berechnet.

In der nachfolgenden Listing wird die Berechnung der Pulslänge in dem Signalgenerator zugrunde liegender VHDL –Code angegeben. Berechnet wird sie nach folgendem Modell:

Pulslänge = 1 + X / 256, wobei X die neue Position darstellt.

Weiterhin gilt: 1 ms < berechnete Pulslänge < 2 ms.

```

if v_COUNTER < 1000000 then

PWM_LEN := PWM_LEN +1;

s_POSITION <= '1';

if PWM_LEN > v_NEW_POS then

s_POSITION <= '0';

end if;

else

v_COUNTER := 0;

PWM_LEN := 0;

end if;

v_COUNTER := v_COUNTER +1;</pre>

```

**Listing 2: Erzeugen von PWM Signale**

Die oben angegebene Listing wird in jedem Takt einmal ausgeführt. Da die Taktlänge 20ns beträgt, entsprechen 1.000.000 Takte genau der Wiederholfrequenz von 50 Hz. Nach jedem Takt wird die Pulsweite "PWM\_LEN" um 20ns erhöht, dabei werden die durchlaufenen Takte in v\_Counter Variable gezählt. Nachdem die Pulsweite die neue Position charakterisierende Länge erreicht hat, wird das Steuersignal "s\_POSITION" auf null gesetzt. Das Steuersignal wird bei jedem Takt verändert, und direkt an der Servosteuerung gesendet.

Die Geschwindigkeitsregelung (mit Hilfe obiger Berechnung) wird so ausgeführt, dass der Variablen "v\_NEW\_POSITION" nicht die endgültige, an den Signalgenerator übermittelte Position übergeben wird, sondern nur ein Zwischenwert. Dadurch werden nach jeder Periodendauer des Steuersignals, leicht veränderte Steuersignale gesendet. Der Zielposition wird also nach jeder Periode, schrittweise angenähert.

#### 3.3 **Simulation**

Die Simulation von digitalen Schaltungen ist eine wichtige Arbeitsphase, die vor der Synthetisierung der entwickelten Schaltung mehrmals durchgelaufen wird. Die Simulatoren unterstützen die Entwickler nicht nur bei der Fehlersuche, sondern helfen auch beim Verstehen von Schaltungen und Signalabläufen. Es gibt mehrere Hersteller von Simulationssoftware, aber das meist etablierte Simulationsprogramm ist ModelSim von Mentor Graphics. In diesem Projekt wird ModelSim als Simulationsprogramm für die VHDL Module eingesetzt. Da die Simulation hauptsächlich automatisiert ablaufen soll, wird ModelSim in Batch Modus ausgeführt.

#### 3.3.1 Benchmarks

Um die entworfene digitale Schaltung zu testen, werden Testbenches verwendet. Sinnvollerweise wird der Testbench in der Sprache erstellt, in der die Schaltung beschrieben wurde. Der Testbench hat keine Bedeutung bei der Synthese von digitalen Schaltungen, er

wird ausschließlich beim Testen eingesetzt. Ein weiteres Merkmal der Testbench ist, das die Entity Deklaration lehr bleibt.

Die wichtigste Aufgabe eines Testbenches ist, die gewünschten Taktsignale, Reset-Signale und falls notwendig Eingangsdaten für die Simulation bereitzustellen. Für die Robotersteuerung sind es die seriellen Daten, die der Testbench mit der angegebenen Übertragungsrate bereitstellt.

Für die Simulation der von den Anwendern erstellten Programme werden Testbenches bereitgestellt, die dann heruntergeladen und modifiziert mit den anderen VHDL Dateien hochgeladen werden können.

#### 3.3.2 Simulationsablauf

Die Simulation der von den Anwendern erstellten VHDL Modellen wird in enger Zusammenarbeit einerseits von der Webschnittstelle, andererseits von der ModelSim Simulationsprogramm durchgeführt. Da die Webschnittstelle als Interface dient, wo man für die Simulation notwendige Parametern eingibt und die zurückgegebene Ergebnisse betrachtet, müssen alle andere Programme, die in der Simulationsausführung beteiligt sind, entweder im Hintergrund ausgeführt, oder als Batch-Programm auf dem Server gestartet werden.

Bevor die Simulation gestartet werden kann, werden die nachfolgenden Parameter über die Webschnittstelle eingegeben, und in der "SIM\_ATTRIBS" Datei am Webserver gespeichert:

• TESTBENCH Name des Testbenches, die bei der Simulation eingesetzt wird

• SIM TIME Simulationsdauer

• SIM START T Ab welchem Zeitpunkt der Simulationsverlauf dargestellt wird

• SIM\_END\_ Ende vom dargestellten Simulationsverlauf

• USERNAME Anwendername (Loginname)

Der "SIM\_ATTRIBS" Datei wird in das "Makefile" inkludiert, bestimmend die Simulationsablauf und die gelieferte Ergebnisse.

#### Simulationsumgebung

Um die Simulation erfolgreich ausführen zu können, wird die UNIX-Umgebung für Windows, das Programm CYGWIN installiert. Mit Hilfe von Cygwin ist es möglich, die von ModelSim bereitgestellten Programme über ein Makefile aufzurufen. Der Simulationsworkflow wird mit Hilfe von Batch-Dateien und Makefiles gesteuert und ausgeführt, wobei der Jobscheduler bei nicht ausreichenden Zugriffsberechtigungen unterstützend eingesetzt wird.

#### Prozesse unter lokalen Zugriffsberechtigungen ausführen

Da die Internetuser nur beschränkte Ausführungs- bzw. Zugriffsrechte haben, ist es nicht möglich, mit der vorhandenen Benutzerrechten von einer Webseite aus die direkte Workflow-

Steuerung abzuwickeln. An dieser Stelle kommt der Jobscheduler zum Zug. In den Makefile, wo Prozesse mit erweiterten Benutzerrechten gestartet werden müssen, werden Batch Dateien ausgeführt, die dann Konfigurationsdateien erzeugen. Basierend auf die so erstellten oder modifizierten Dateien, führt der Jobscheduler mit lokalen Anwenderrechten die Simulationsschritte aus. Um den Workflow-Ablauf nicht zu unterbrechen, werden Watch-Dog Signalen verwendet, die nach einer Zeitüberschreitung der Simulationsausführung die Abarbeitung von Makefile fortsetzt.

./sim\_vsim.bat \$(TESTBENCH) > /cygdrive/c/inetpub/wwwroot/Robot4Web/reports/start\_vsim.sh waitfor /T 60 contvsim

#### Listing 3: Verwendung von Watch-Dog Signale in ein Makefile

In der oben dargestellten Listing wird die Datei "start\_vsim.sh" erstellt, und anschließend die Simulation vom Jobscheduler gestartet. Bei Erfolg werden "waitfor /SI contvsim" vom Jobscheduler gestarteten Batch-Dateien ausgeführt, signalisierend für die wartenden Prozesse die Weiterführung.

Sobald alle vom Jobscheduler aufgerufenen Prozesse beendet sind, wird die Workflow-Ausführung mit eingeschränktem Zugriff weiter ausgeführt. Unter Windows Vista verwendet Cygwin das Konto "NetworkService", um Befehle mit eingeschränktem Zugriff auszuführen.

#### **ModelSim Befehle**

ModelSim stellt eine große Anzahl von Befehlen bereit, die in Batch Modus ausgeführt werden können, wodurch eine Automatisierung von der Simulation möglich gemacht wird. In diesem Projekt wurden die nachfolgenden ModelSim Befehle eingesetzt: vsim, vlib, vcom, und vmake.

Mit "vlib" können ModelSim Bibliotheken erstellt und anschließend kompiliert werden, dann werden sie für die nachfolgende Simulation eingebunden. In unserem automatisierten Simulationsablauf wird "vsim" verwendet, um das "work" Bibliothek zu erstellen.

Der Befehl "vcom" kompiliert die gefundenen VHDL Dateien in die spezifizierte Bibliothek, oder in die standardmäßig eingestellte "work" Bibliothek.

Da bei der Kompilierung von VHDL Codes die Abhängigkeiten zwischen den Komponenten häufig nicht berücksichtigt werden können, wird der Befehl "vmake" aufgerufen, um ein "makefile" zu erzeugen, in dem die Komponenten in (meistens) richtiger Reihenfolge abgearbeitet werden.

Mit dem Befehl "vsim" und der anschließender Benchmark-Name wird die Simulation gestartet. Die bei der Ausführung aufgetretenen Fehlermeldungen werden in die Transcript-Datei abgespeichert, und später im Simulationsbericht über die Webschnittstelle aufgerufen.

Neben den vorher erwähnten ModelSim Befehle wird noch das "simulate.do" Datei mit "vsim -do simulate.do" aufgerufen. In diesem Fall werden alle in "simulate.do" Datei befindliche Befähle hintereinander ausgeführt[8].

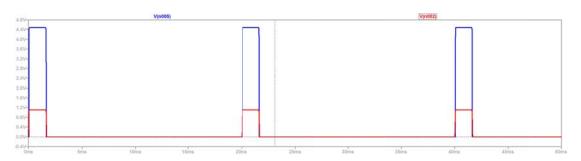

### 3.3.3 Ergebnisse der Simulation

Die Ergebnisse der Simulation werden über einer Berichtseite für die Anwender zugänglich gemacht. Nur authentifizierte Anwender können Zugang zu eigene Testberichte erlangen. Nach jeder Simulation werden die vorangegangenen Ergebnisse überschrieben.

Die simulierten Signalverläufe für die festgelegten Zeitrahmen werden in ein JPG und ein PS Datei abgespeichert. Im Testbericht ist noch das von ModelSim erstellte "Transcript", das Simulationsreport und die "vsim.wlf" Datei aufgelistet.

# 3.4 Hardware Synthese

Ziel der Hardware Synthese ist eine möglichst schnelle und kostengünstige Synthese, um digitale Schaltungen in eine FPGA zu realisieren. In der Praxis verwendete Synthesewerkzeuge ermöglichen die Erkennung von Fehlern im Design, die durch die Simulatoren unentdeckt bleiben, weil der Code syntaktisch korrekt ist. Aus diesem Grund empfiehlt es sich die Verwendung von Synthesewerkzeugen, und zwar bereits in einer früheren Entwurfsphase[12].

Zur Synthese von VHDL Modellen in Virtex II-Pro und in Spartan 3A des FPGAs wird das Windows basierte Synthesewerkzeug Synplify Pro von der Firma Synplicity verwendet. Dazu wurde auf das Betriebssystem Windows Vista das Programm Synplify Pro mit der Einbindung des Lizenzservers des Instituts ICT der Technischen Universität Wien installiert.

## 3.4.1 Syntheseablauf

Die Synthese von digitalen Schaltungen ist die automatische Umsetzung einer Darstellung der Schaltung auf einer Abstraktionsebene, in eine Darstellung auf die nächst tiefere Abstraktionsebene. Die Umsetzung wird in mehreren Schritten durchgeführt, die in zwei Syntheseebenen mit unterschiedlichen Technologieabhängigkeiten zusammengefasst werden können. In der technologieunabhängige "High-Level Synthese" wird die algorithmische Ebene auf die RT-Ebene übersetzt(engl.: RTL Translation). Die nachfolgende Logikoptimierung versucht nun die im ersten Schritt gewonnene technologieunabhängige Realisierung so umzuformen, dass eine optimale Umsetzung in die Zieltechnologie im Rahmen der Technologieabbildung möglich ist. Integraler Bestandteil der beiden letzten Schritte ist die Timing-Analyse. Nach der Technologieabbildung liegt eine optimierte Netzliste mit Bauelementen der Zieltechnologie vor, die dann platziert und verdrahtet werden kann[12].

### 3.4.2 Eingabedaten

Für die Synthese, ähnlich wie bei der Simulation, werden die VHDL Modelle geladen und kompiliert. Da die Synthese nur teilweise technologieunabhängig durchgeführt wird, sind weitere Informationen über das Zielsystem und die verwendete Technologie an das Synthesewerkzeug zu übergeben. Diese Informationen werden zur Steuerung der RTL-Synthese eingesetzt, die die RT-Ebene auf die technologieabhängige Gatter-Ebene übersetzt.

Die Übergabe von VHDL Dateien und herstellerspezifische Informationen an das Synthesewerkzeug Synplify Pro geschieht mit Hilfe einer Projekt-Datei. Die Projektdatei wird vor dem Synthesebeginn erstellt und besteht aus einem generierten und aus einem statischen Teil. Der generierte Teil beinhaltet die Pfade und die Dateinamen aller VHDL Dateien, die während der Synthese verwendet werden. Der statische Teil von der Projekt-Datei beinhaltet die Implementierungsoptionen über Hersteller, Technologie, Geschwindigkeit und Package, sowie Angaben zur Steuerung der Syntheseablauf. Da der letzte Teil der Projekt-Datei den Projektablauf und die verwendete Technologie beschreibt, werden diese Informationen nur von dem Systembetreuer verwaltet.

### 3.4.3 Syntheseergebnisse

Das Ergebnis der Synthese ist eine Netzliste, die die Verbindung zwischen den FPGA Bausteinen, wie LUT, Flipflops, MUX, etc. beschreibt. Weil das Ergebnis der Synthese sich auf der Gatterebene befindet, können Signale und Ports auf der Gatterebene nur noch binäre Werte annehmen.

Die Netzliste, als Ergebnis von der Synplify durchgeführte Logiksynthese, wird in EDIF-Format(Electronic Design Interchange Format) abgespeichert, und in den weiteren Schritten von den in Xilinx ISE 9.2 enthaltenen Werkzeugen importiert. Der geloggte Syntheseablauf, und die von Synplify erstellten Berichte werden letztendlich auf die Berichtseite zusammengefasst, und den Erstellerbenutzer zugeordnet.

#### 3.5 Bitstrom erstellen und hochladen

Zum Konfigurieren des FPGAs wird das Windows-basierte Entwicklungskit ISE 9.2 von Xilinx verwendet. Dazu wurde auf einem Windows-Betriebssystem die Entwicklungs-umgebung installiert, und das vorhandene Workflow für die Simulation und Logiksynthese so erweitert, dass die Ergebnisse der vorangegangenen Schritte wiederverwendet werden können.

Bevor die FPGA Kofigurationsdatei(eng.: Bitstream) hochgeladen werden kann, werden von der Synthese erzeugten EDIF-Datei ausgehend noch weitere Zwischenschritte, wie das Übersetzen des Sourcecodes in eine NGD-Datenbank, Place and Route, usw. durchgeführt.

Zusätzlich sind noch das Programmierkabel, die FPGA Pin-Zuordnung und die Taktrate zu konfigurieren.

### 3.5.1 FPGA Pin-Zuweisung

Da die bisher entwickelte Modelle nur die FPGA interne Abläufe beschreiben, müssen die Schnittstellen definiert werden, wodurch der FPGA im Stande ist, die interne Schaltungen zu Takten, Signale zu empfangen und zu versenden. Die Definition dieser Schnittstelle ist vom Hersteller und von Modell abhängig, deswegen wird sie in einer vom Anwender konfigurierbare Datei zusammengefasst.

Eine UCF(User Constraints File) Datei ist eine vom Benutzer erstellte ASCII Datei, die Einschränkungen auf dem funktionellen Entwurf spezifiziert. Nachfolgend wird der TOP.UCF Dateiinhalt aufgelistet.

Listing 4: Zuweisung von Virtex II-Pro I/O-Ports an das R4W Design und Taktbestimmung

In der oben dargestellten Datei wird die Zuordnung zwischen den Schnittstellen des VHDL-Modells (Ein- und Ausgänge der Top-Level-Entity) und den Schnittstellen des FPGA mit der Peripherie (Pins des FPGA) festgelegt. Die Zuweisung der Pins erfolgt mittels sogenannter "Pin Assignments"[15][17].

#### 3.5.2 Von der Logiksynthese zum Bitstrom

Das Ergebnis der Logiksynthese wurde vom Synthesewerkzeug Synplicity erstellt; nun wird die Netzliste in die Xilinx ISE Umgebung importiert, um die nächsten Schritte Richtung physikalische Realisierung zu absolvieren. ISE hat ein eigenes Synthesewerkzeug(XST), die Synplicity aber bietet einige Vorteile, die für diese Arbeit unverzichtbar sind.

Die nachfolgenden Schritte sind in ein Makefile zusammengefasst, und werden mit Hilfe von "make" automatisiert ausgeführt. Bei der Ausführung verwendete Befehle gehören zur ISE Entwicklungsumgebung, und werden in Batch Modus ausgeführt.

#### **NGD-Datenbasis**

Die NGD-Datenbasis ist eine logische Datenbasis, in der das erstellte VHDL Design als hierarchische Verschaltung von Xilinx-Komponenten-Makros dargestellt wird. Die Datenbasis wird mit Hilfe von "ngdbuild" erstellt. Die Einstellungen in der UCF-Datei werden ebenfalls mit "ngdbuild" in der NGD-Datenbasis eingetragen.

#### **Technologie-Mapping**

Die Abbildung der minimierten Schaltfunktionen und von der Xilinx-Komponenten-Makros auf die Ziel-FPGA ist ein sehr rechenintensiver Vorgang. Hier werden in der Netzliste definierte logische Schaltungen auf reale physikalische Schaltungen, die in der FPGA vorhanden sind, abgebildet. Dabei wird versucht Platz zu sparen, und um das Zeitverhalten der Schaltung zu verbessern, die miteinander verbundene LUTs und Flipflops so in CLBs zu verpacken, dass die Gesamtverdrahtungslänge minimal ausfällt. Die Technologie-Mapping wird mit Hilfe vom in ISE Entwicklungsumgebung enthaltenen "map" Programm ausgeführt.

#### **Place and Route**

Bei Platzierung und Verdrahtung der Technologieelemente werden heuristische Algorithmen verwendet, um optimale Ergebnisse zu erzielen. Aus diesem Grund sind die Kosten für diesen Technologieschritt schwer abzuschätzen. "Place and Route" wird in zwei sukzessive Schritte ausgeführt: Platzieren und Verdrahten. Beide Prozesse sind sehr rechenintensiv, und haben als Ziel eine optimale Platzierung zu finden, und anschließend so zu Verdrahten, dass möglichst alle (zeitliche)Randbedingungen erfüllt werden können. Die Ergebnisse vom "Place and Route" haben einen großen Einfluss auf die Performance der Schaltung.

Das Programm "par" führt die Platzierung und Verdrahtung der in der Netzliste definierten Komponente aus.

#### Bitstreams erstellen

Der Bitstrom wird mit Hilfe des ISE-BitGen-Programms aus NCD-Datei erzeugt. Eine NCD-Datei ist ein vollständig platziertes Design, eventuell mit Routing-Informationen ergänzt. Das Ergebnis ist eine FPGA-Konfigurationsdatei(Bit-Datei), die noch verschlüsselt und direkt in die FPGAs geladen werden kann[18].

## 3.5.3 Programmieren vom FPGA

Sind die Bitströme erzeugt, dann können diese Konfigurationsdateien mit Hilfe von Xilinx bereitgestelltes Tool iMPACT in der FPGAs im Boundary Scan Mode neu konfiguriert werden. Dabei werden im FPGA physikalische Verbindungen zwischen den einzelnen FPGA Komponenten entsprechend der Netzliste hergestellt. Die Verbindungen entstehen durch die programmierbaren Schalter, die die entsprechende Leitungssegmente zusammenschalten. In dieser Phase werden noch zusätzliche Optimierungen vorgenommen, um die entstehende Pfade zu minimieren, und gleichzeitig die Timing-Bedingungen zu erfüllen. Neben der Verdrahtung werden die LUTs mit den berechneten Werten oder mit Boole'schen Gleichungen initialisiert.

Die Konfiguration der FPGAs wird mit Hilfe vom Xilinx Programmier- und Debuginterface Parallel Kabel IV über die JTAG-Schnittstelle vorgenommen. Xilinx Spartan 3A verwendet ein USB-Kabel, um die Programmierung der FPGAs durchzuführen. JTAG ist die Bezeichnung für den von der Joint Test Action Group entwickelten Standard IEEE 1149.1.

### 3.6 **FPGA Sicherheit**

"Die Virtex-II-Pro-Bausteine besitzen eine integrierte Entschlüsselungs-Engine, die sich zur Sicherung des Konfigurations-Bitstroms und damit auch des FPGA aktivieren lässt. Den Bitstrom verschlüsselt man in der Xilinx-Software mit Hilfe eines Schlüsselsatzes, und das Virtex-II-Pro-Bauteil entschlüsselt den einlaufenden Bitstrom intern, anhand des gleichen Schlüsselsatzes.

Sobald das Design in den ISE-Tools einen Platzierungs- und Routinglauf hinter sich hat, wird der verschlüsselte Konfigurations-Bitstrom anhand des ISE-BitGen-Programms mit benutzerdefinierten Schlüsseln generiert. Die gleichen Schlüssel werden über den JTAG-Port mit Hilfe der ISE-iMPACT-Tools in das FPGA geladen.

Um den Schlüssel in den Baustein zu programmieren, muss dieser in den Key Access Modus versetzt werden, der das FPGA automatisch löscht – einschließlich aller alten Schlüssel und des aktuellen Bitstroms. Auch diese Maßnahme bietet Schutz gegenüber Angriffen.

Nachdem der Baustein mit den Schlüsseln programmiert ist, kann man ihn mit dem verschlüsselten Bitstrom konfigurieren. Sobald der verschlüsselte Bitstrom in das FPGA programmiert ist, lässt sich dieses weder durch unbeabsichtigte noch durch beabsichtigte Eingriffe oder Einbrüche rekonfigurieren, partiell konfigurieren oder auslesen. Jeder Versuch, ein Design zu stehlen, führt automatisch zur Löschung des gesamten FPGA (für Test- und Debugging-Zwecke lassen sich allerdings nicht-verschlüsselte Bitströme in ein FPGA programmieren, wo im vornhinein Schlüssel geladen wurden).

Die Schlüssel sind in einem speziellen Dreifach-DES-Block an einer Ecke des Bauteils angeordnet. Eine externe Batterie dient zur Speicherung der Schlüssel, wenn die Leiterplatte nicht unter Spannung steht. Jede normale Batterie mit einer Spannung zwischen 1 und 4 V lässt sich verwenden; das ermöglicht eine Lebensdauer von 15 Jahren.

Obwohl nicht-flüchtige PLD-Sicherheitsbits Lese-/Schreibzugriffe auf den Bauteil sperren, bietet die Dreifach-DES-Funktion von Virtex-II Pro mit Verschlüsselung echte Sicherheit. Und selbst wenn die Anordnung des Dreifach-DES-Blocks in den Virtex-II-Pro-FPGAs bekannt ist, lassen sich die Schlüssel ohne eine Löschung des Chips nicht abfangen.

Eine weitere Schutzbarriere gegen potenzielle Diebe sind neun Metall-Schichten. Weil bei der Speicherung der Sicherheitsbits keinerlei feste Verdrahtung beteiligt ist, sind sämtliche Versuche zum Scheitern verurteilt, die in den Virtex-II-Pro FPGAs verborgenen Sicherheitsbits per Wärmebildtechnik zu finden." [13]

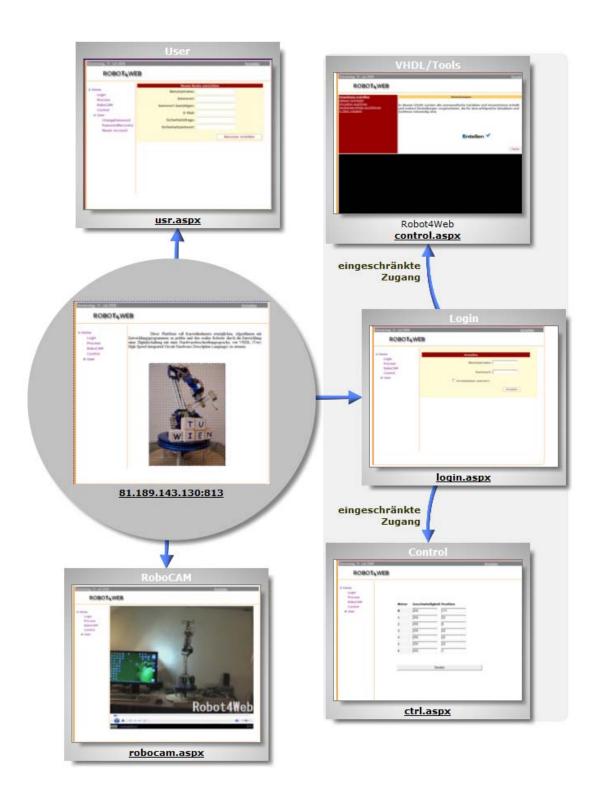

Das Projekt Robot4Web ist so geplant und ausgeführt, dass die Anwender über das Internet alle notwendigen Schritte für die Steuerung des Roboters bzw. die Simulation und Synthese von VHDL - Codes ausführen können. Die hier beschriebene Webschnittstelle erlaubt es, all diese Aufgaben über eine grafische Weboberfläche zu steuern.

Um diese umfangreichen Aufgaben erledigen zu können, ist noch zusätzlich eine auf Rollen basierende Anwenderverwaltung dazugefügt. Die Website basiert auf Microsoft.Net Technologie, und läuft auf ein Microsoft Internet Information Server(IIS 7) Webserver unter Windows Vista.

Dieses Kapitel behandelt den Entwurf und die Funktionsweise aufgabenspezifischer Schnittstellen.

# 4.1 Zugriffskontrolle und Anwenderverwaltung

Wenn bestimmte Personen keine Zugriffsberechtigung auf R4W Webseite haben, muss ihnen der Zugriff auf die entsprechende Schnittstelle verweigert werden. Um die richtigen Zugänge zu gewähren, werden die Nutzer in drei Gruppen geteilt, und die entsprechenden Rollen über die Rollenverwaltung zugeordnet. Demnach wird folgende Rollenteilung aufgestellt:

- Nutzer, die nur surfen dürfen, aber sonst keine Dienste nutzen sollen,

- Anwender, die Programme bedienen, und den Roboter steuern dürfen,

- Administratoren mit erweiterten Befugnissen.

Für die Nutzer sind keine Verwaltungsmaßnahmen zu treffen, da für diese Gruppe grundsätzlich kein Zugang in das sensible Bereich gewährt wird. Anwender müssen einen Eintrag in der Benutzerverwaltung haben, und sind in der Rolle "user" zusammengefasst. Administratoren bekommen über die Benutzerverwaltung weitere Rechte zugewiesen, der verwendete Rollenname ist "admin". Die erteilten Zugriffsberechtigungen sind in den WEB.CONFIG Dateien gespeichert. Da die Website in Verzeichnissen strukturiert ist, wird in jedem Webseitenverzeichnis ein WEB.CONFIG Datei erstellt, in dem die Zugriffsberechtigungen auf diese Verzeichnisse erteilt beziehungsweise verweigert werden.

Um die Anwender und Administratoren zu erkennen, um diesen Personen die zugewiesenen Ressourcen freizugeben, wird eine formularbasierte Authentifizierung verwendet. Für formularbasierte Authentifizierung werden die anwenderspezifische Daten wie: Anwendername, E-Mail, Passwort usw. in einer SQL-Express Datenbank erfasst. Für die erfolgreiche Identifizierung sind Passwort und Anwendername notwendig. Die Datenbankdatei mit Benutzerkonten und mit der Definition bestimmter Rechte ist in "App\_Data"Verzeichnis auf dem Webserver abgelegt.

Die Zugriffskontrolle bietet weiterhin die Möglichkeit, verlorene Passwörter durch neu generierte zu ersetzen, oder bestehende Passwörter zu verändern. Die eingegebenen Anwenderdaten werden zusätzlich noch dazu benutzt, um für jeden Anwender ein Verzeichnis zu erstellen. In diese Verzeichnisse werden die hochgeladene VHDL - Programme und die vom System generierte Rückmeldungen gespeichert.

Durch die Webschnittstelle kann ein Administrator sehr einfach Anwendern Zugang gewähren beziehungsweise entziehen.

# 4.2 **Streaming**

Um die Roboterbewegungen zu verfolgen, werden in der Projektumgebung Webcams verwendet, die die erfassten Bewegungen des Roboterarms über das Internet bereitstellen.

Neben der verwendeten Webcams wird noch das Streamingprogramm G4 eingesetzt, um gespeicherte Videoaufnahmen für didaktische Zwecke wiederzugeben. Zusätzlich kann man das Programm G4 einsetzen, um Webcams ohne integrierte Webserver, "live Streaming" zu ermöglichen. Streamingprogramme übertragen einen kontinuierlichen Fluss von Video- bzw. Audiodaten zwischen Webserver und Client. Im Project Robot4Web wird ein in MPEG Format codierte Datenübertragung verwendet.

Die eingesetzte Linksys WVC54GC Webcam bietet Webserver-Funktionalität, und ermöglicht die direkte Bildübertragung über das Internet. Die Kamera sendet einen Videostream kodiert mit MPEG 4 bei einer Auflösung von 320 x 240 Pixeln. Die Kamera kann auch auf Bewegungen im Raum reagieren, mit einer Aufzeichnung beginnen, und den Administrator oder die Anwender per E-Mail oder SMS informieren. Da die Linksys WVC54GC Webcam eine geringe Auflösung hat, eignen sich von der Kamera bereitgestellte Bilder nicht für weitere Bildverarbeitung. Die bereitgestellte Funktionalität wird für Dokumentierung von Roboteraktivitäten verwendet.

Das Programm G4 von der Firma "CT-Tech GbR" ermöglicht das Versenden übers Internet bis zu vier Videoströmen gleichzeitig. Die wichtigste Eigenschaft des Programms ist aber, dass Videostream in hohe Auflösung gesendet werden können. Durch die eingesetzte Encoder-Technologie ermöglicht das Programm die live - Übertragung von Audio- und Videosignalen in DVD-Qualität. Um gleichzeitig aufgezeichnete Videodaten und Webcam-Ströme senden zu können, werden bis zu vier, von Port 80 abweichende Ports verwendet. Mit Hilfe

einer hochauflösenden Kamera, ermöglicht das Programm die gewonnenen Videoströmen über Musterkennungsprogramme zu bearbeiten und auszuwerten.

Um die gesendete Streaming nutzen zu können, ist auf der Empfängerseite ein Wiedergabeprogramm zu installieren, das entweder ein in Webbrowser integrierte Plug-in ist, oder auch ein eigenständiges Wiedergabeprogramm. Für die MPEG - Format ist die Windows Media Technologie-Plattform zu empfehlen.

# 4.3 Simulation und Synthese

Die Webschnittstelle, in Zusammenarbeit mit dem Job Scheduler, ermöglicht die Simulation und Synthese von bereitgestellten VHDL - Programmen. Dazu werden die von den Anwendern erstellten VHDL - Dateien auf dem Webserver geladen. Das Hochladen von Programmen oder die Datenübermittlung für die Robotersteuerung wird über die Webschnittstelle abgewickelt. Die Daten können mit einem Zippprogramm komprimiert, oder aber in nicht komprimierter Form übertragen werden. Das System erkennt automatisch die komprimierten Daten, und entpackt sie im anwenderspezifischen Verzeichnis.

Die Simulation und die Synthese von VHDL - Codes müssen nicht zwingend auf demselben Rechner ausgeführt werden, wo die Webserver-Applikationen laufen. Dieses zu entscheiden, ist die Aufgabe des Job Schedulers, mit dessen Hilfe Applikationen auf anderen Rechnern im selben Netzwerk ausgeführt werden können.

Um diese Interfaces benutzen zu können ist es erforderlich, dass die Anwender sich am Server authentifizieren. Bei dem Authentifizierungsvorgang werden die eingegebenen Daten mit den Anwender-Daten aus der Datenbank verglichen, und der Zugang wird mit den zugewiesenen Rechten gewährt. Die Daten für die Anwenderverwaltung kann man aus der Zentralen TU-Datenbank beziehen, oder es wird einfach überprüft, ob der User von einer TU-Wien - Webseite kommt, wo er schon im Vorfeld eine Authentifizierung erfolgreich ausgeführt hatte.

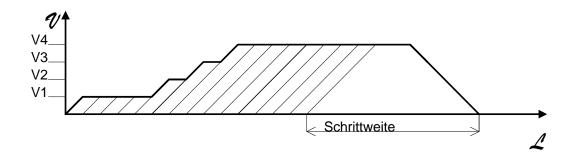

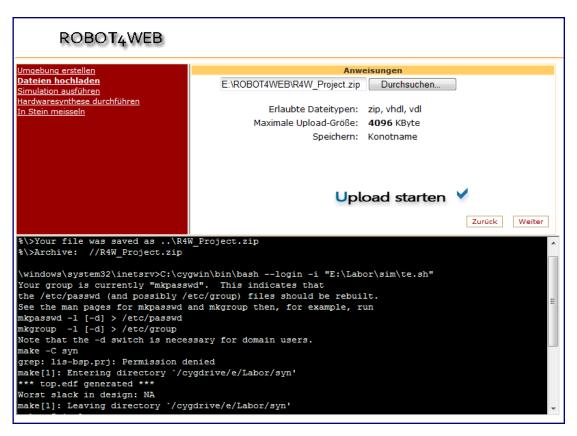

Abbildung 8: Webschnittstelle für Simulation und Synthese von VHDL - Dateien.

## 4.3.1 Seitenaufbau

Die für die Simulation und Synthese entworfene Webschnittstelle ist in drei Bereichen unterteilt, und besteht aus einem Navigationsteil, einem Bedienfeld und einem Ausgabefenster.

Die Navigationshilfe ermöglicht die Orientierung auf der grafischen Oberfläche, und die direkte Auswahl einzelner Zwischenschritte.

Das Bedienfeld beinhaltet zusätzliche Hinweise bzw. Anweisungen, die bei der Ausführung des gewählten Schrittes zu beachten sind. Für jede Ausführungsphase erscheint ein neues Bedienfeld mit dem, für diese Phase notwendigen Optionen. Mit Hilfe von Navigationsbuttons kann man Schritt für Schritt den gesamten Erstellungsprozess durchlaufen lassen, oder bestimmte Zwischenschritte wiederholen.

Das Ausgabefenster ist wie ein DOS-Shell designt, und soll dem Anwender das Gefühl vermitteln, dass die Programmausführung in einer Kommandozeilenebene stattfindet. Das Ausgabefenster bekommt alle Meldungen von den ausgeführten Prozessen, einschließlich solche Fehlermeldungen, die über den "standard error"-Stream geschickt wurden. Da die Programmausführungen über Kommandozeilenaufrufe abgewickelt werden, ist nicht schwer, die stderr Stream (also Standard Error) mit Hilfe von Pipelines umzuleiten und anschließend in das Ausgabefenster zu kopieren.

## 4.3.2 Zwischenschritte für Simulation und Synthese

Um Bitströme über die Webschnittstelle aus VHDL-Modellen zu erzeugen und anschließend in den FPGA zu laden, sind fünf sukzessive Schritte auszuführen. Jeder einzelner Schritt ist direkt aufrufbar, was die erneute Ausführung erfolgreich absolvierten vorangegangenen Vorgängen überflüssig macht.

## Umgebung erstellen

In diesem Schritt werden alle Anwenderspezifische Variablen und Verzeichnisse erstellt, und weitere Einstellungen vorgenommen, die für eine erfolgreiche Simulation und Synthese notwendig sind. Die Ergebnisse dieses Schrittes werden umgehend im Ausgabefenster angezeigt. Die Erstellung der anwenderspezifischen Umgebung ist nur einmal auszuführen, und bleibt solange bestehen, bis der Administrator diese Daten löscht. Der Anwender wird jedenfalls darüber benachrichtigt, ob die Umgebung erstellt wird oder bereits existiert. Auf Abbildung 4 ist folgendes ersichtlich: der Anwender wird darüber informiert, dass das zu erstellende Verzeichnis bereist existiert.

### Dateien hochladen

Über die, auf Abbildung 5 gezeigte Webschnittstelle kann man die Projektdateien hochladen. Bei dieser Übertragung handelt es sich nicht um FTP-, sondern HTTP-Datenübertragung; im Zuge dessen wird die maximale Upload-Größe auf 4MB eingeschränkt. Nach der erfolgreichen Datenübertragung wird serverseitig überprüft, ob die hochgeladene Dateien komprimiert sind. Falls es sich um eine ZIP-Datei handelt, wird diese anschließend ausgepackt. Bei der Dekomprimierung von ZIP-Dateien werden die, vom ZIP-Programm generierte Meldungen über dem Ausgabefenster zurückgegeben. Dazu ist es notwendig, dass das Programm zum Entpacken von komprimierten Dateien - in diesem Fall das UNZIP Programm - am Webserver vorinstalliert ist.

Im nachfolgenden Codeausschnitt wird die als Parameter übergebene Datei entpackt, dabei wird der Stream der Standardfehlerausgabe (stderr) so umgeleitet, dass gemeinsam mit der Standardausgabe geloggt werden kann:

@echo off unzip -u %1 -d %2 2>&1

### Simulation ausführen

Um eine VHDL - Modell zu simulieren, wird Modelsim verwendet. Modelsim wandelt mit Hilfe des VHDL - Compilers die VHDL Codes in eine für den Simulator verständliche Form um, dabei wird die Syntax des Codes überprüft, und nach vorhandenen Bibliotheken gesucht. Die gefundenen Bibliotheken werden zu Simulation von Modelsim geladen. Um die zu be-

trachtende Signale festzulegen, und um die Simulation ausführen zu können, muss der Anwender ein Testbench erstellen.

Für die Simulation über die Webschnittstelle werden Kommandozeilenaufrufe verwendet. Diese Kommandos sind ausführbare Programme, und lassen sich von einer Unix-Shell aus, ohne grafische Oberfläche von Modelsim, aufrufen. Die erzeugten Meldungen werden über dem Ausgabefenster dargestellt. Falls Dateien oder Grafiken erstellt werden, dann sind diese in dem Verzeichnis abgespeichert, der für den Anwender eingerichtet ist. Die Anwender haben dann später die Möglichkeit, die von Modelsim generierten Dateien herunterzuladen und zu analysieren.

## Hardwaresynthese durchführen

Nachdem mit Hilfe der funktionalen Simulation die Korrektheit des FPGA-Designs überprüft ist, wird das Design synthetisiert. Als Synthesewerkzeug wird Synplify von Synplicity, oder ISE von Xilinx verwendet. Beide Programme lassen sich gleichzeitig einsetzen, da ISE-Projekte die Einbindung von Synplify als Synthesewerkzeug erlauben.

Durch das Auswählen vom Menüpunkt "Synthese Starten" im Navigationsbereich wird die Simulation durch den Webinterface angestoßen. Tatsächlich wird eine Datei auf dem Webserver angelegt, die die Simulation beschreibt. Die Erzeugung dieser Datei veranlasst den Jobscheduler, die Hardwaresimulation auszuführen. Die endgültige FPGA-Implementierung wird jedoch noch nicht festgelegt. Das Ergebnis der Synthese ist die Netzliste, die für die Generierung der Bitströme weiter verwendet wird.

Wie bei den vorangegangenen Schritten, werden die erzeugte Meldungen im Ausgabenfenster wiedergeben.

## Bitströme generieren

Nachdem die Simulation und die Hardwaresynthese erfolgreich abgeschlossen sind, werden die Bitströme generiert, und anschließend in den Virtex II Pro FPGA geladen. Die Generierung der Bitströme ist der letzte Schritt, den man absolvieren muss, um von VHDL – Modellen zum endgültigen Programm zu gelangen.

Ein FPGA wird konfiguriert, indem seine Architekturelemente mit den geeigneten Konfigurationsbits belegt werden. Die Gesamtheit aller Konfigurationsbits, gemeinsam mit den herstellerspezifischen Konfigurationsdaten, bezeichnet man als Bitstrom (Bitstream).