# Design refinement for wirless sensor networks (using SystemC AMS extensions)

Institut für Computertechnik

#### ICT

Institute of Computer Technology Univ.Prof. Dr. habil. Christoph Grimm Chair Embedded Systems Vienna University of Technology

Heinz Zemanek and his "Mailüfterl": First transistor computer. (TU Vienna/ICT, 1955)

## Computer Technology

Today, computers are very small and very cheap – the end of development?

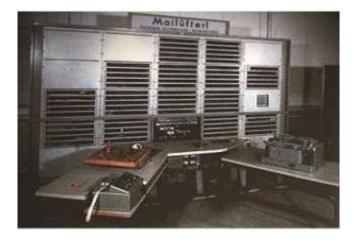

### More than Moore!

WIEN

### Wireless ultra-low power sensor networks

#### Introduction

- Design challenges

- OSCI SystemC AMS extensions

- Support for refinement of sensor networks

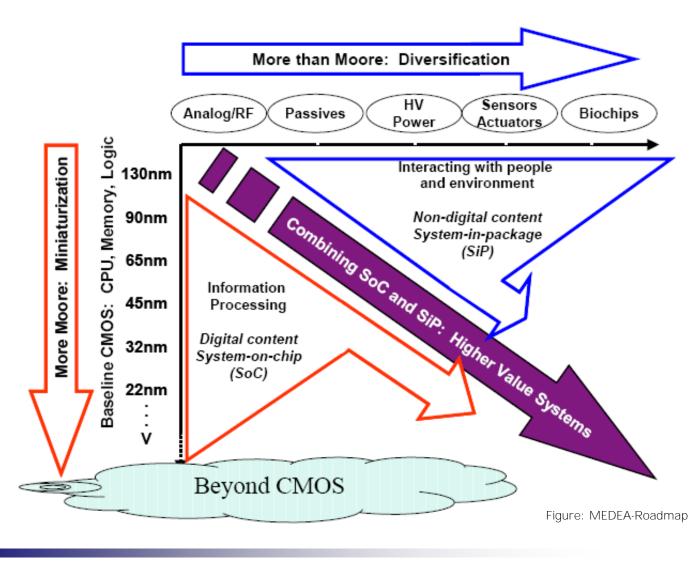

## Sensor networks (e.g. in ambient assisted living)

Alarm & Rescue Centre

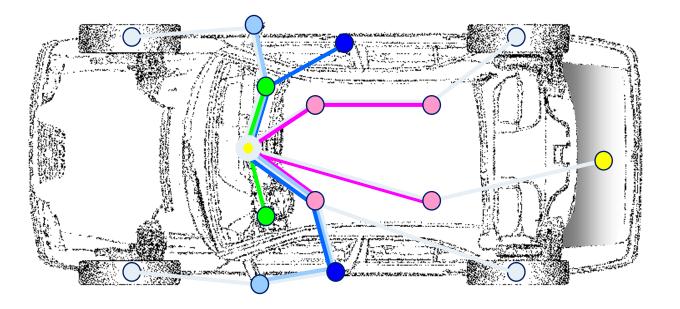

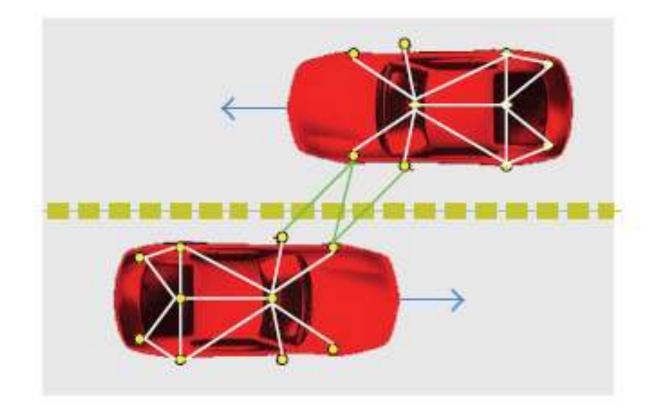

## Sensor networks (e.g. in automotive application)

Tire pressure metering ...

- Sensors will be embedded in tire and "harvest" energy

- Multi-hop protocol increases dependability

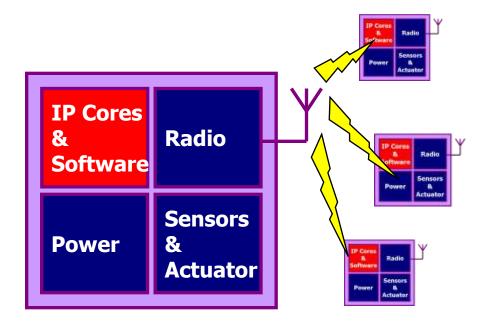

## Ultra-low power wireless sensor network

### (Ultra-low power wireless) "Sensor networks"

- Growing interest from industry

- Energy autonomy for "lifetime"

### Some typical requirements:

- mikrowatt radio (average consumption: some uA)

- Iow duty cycle (< 1%)</p>

- Iow throughput (1-10kbps)

- Often helpful: very cheap, very small …

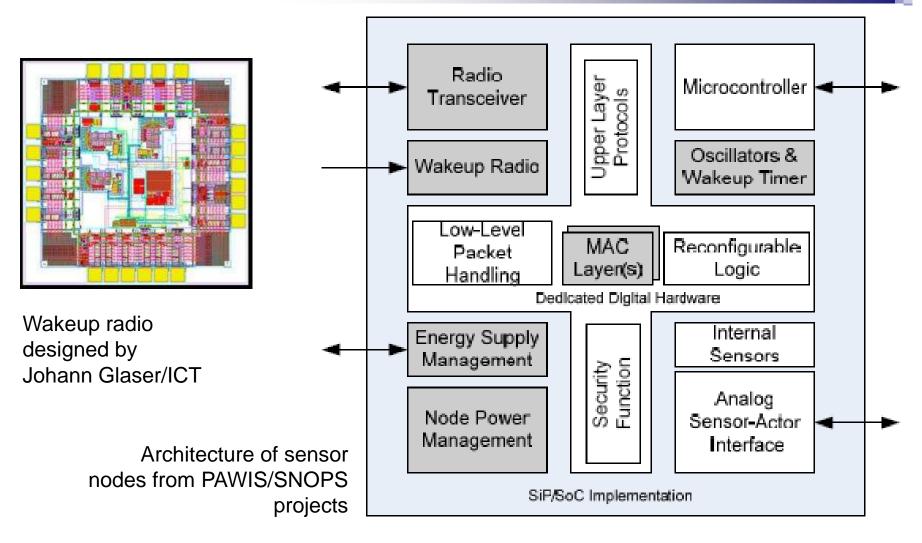

## Ultra-low power wireless sensor network node

### **Typical ingredients**

- Sensing unit

- Signal conditioning

- ADC, DAC

- DSP

- Protocol Stack (e.g ZIGBEE simplified/adapted)

- Energy harvester , energy scavenging e.g. Solar cell, Antenna, MEMS, ...

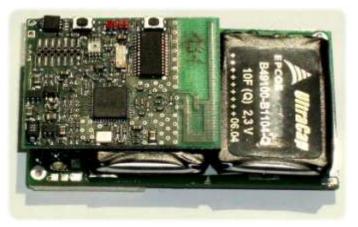

# Architecture from ICT's PAWIS node

### Wireless ultra-low power sensor networks

- Introduction

- Design challenges

- OSCI SystemC AMS extensions

- Support for refinement of sensor networks

- Process technology: Tradeoff size leakage current

- Analog/digital partitioning

- Voltage matching problem: Combination of different technologies requires different voltages

- DC/DC converters & Power management: very low quiescent current!

- Oscillator start-up time

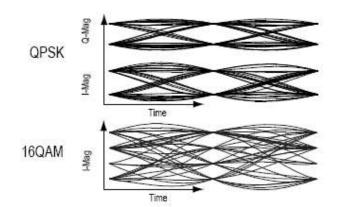

- Choice of modulation scheme

- ON/OFF, ASK: simple + very energy efficient hardware, but not robust against noisy environment

- FSK, more complex ones: less simple, but more robust at higher data rates

- Combinations: Wake-up, control: ASK; rest: FSK+...

- Wakeup problem

- Optimization at protocol level

- Multi-hop protocols star network architecture

- Which offers appropriate performance at lowest cost/power consumption?

## Even much more than More than Moore

. . .

Network level OMNET++?

- Functional level Simulink, Ptolemy, ...

- Architecture level SystemC? AMS extensions?

- Block level, circuit level VHDL-AMS, Verilog-AMS,

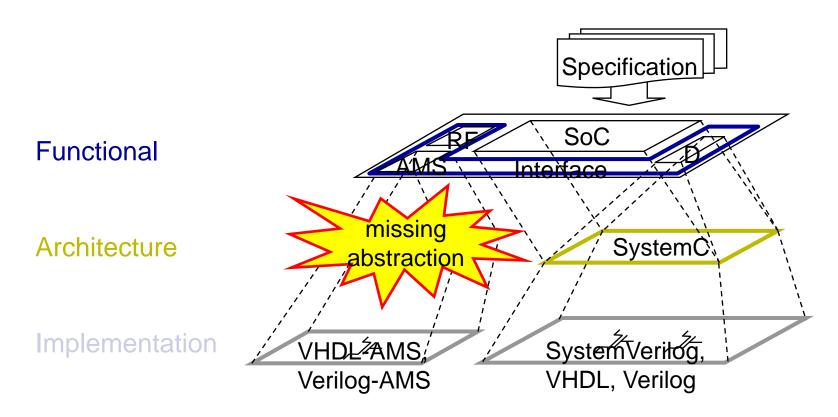

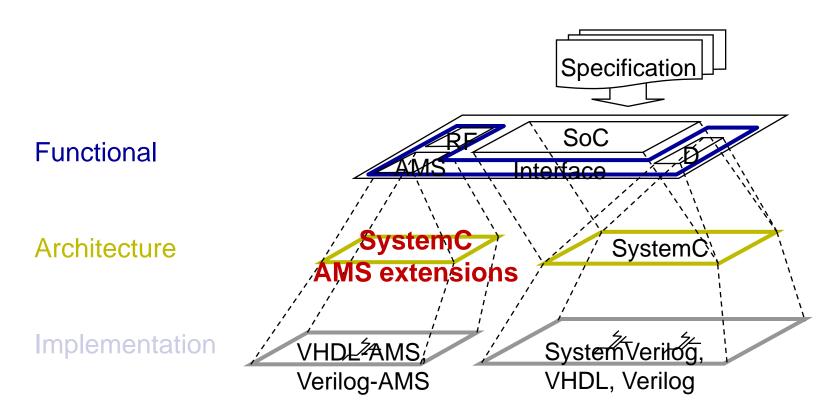

### Gap at architecture level

C. Grimm - Design Refinement for Wirless Sensor Networks

### Gap at architecture level

C. Grimm - Design Refinement for Wirless Sensor Networks

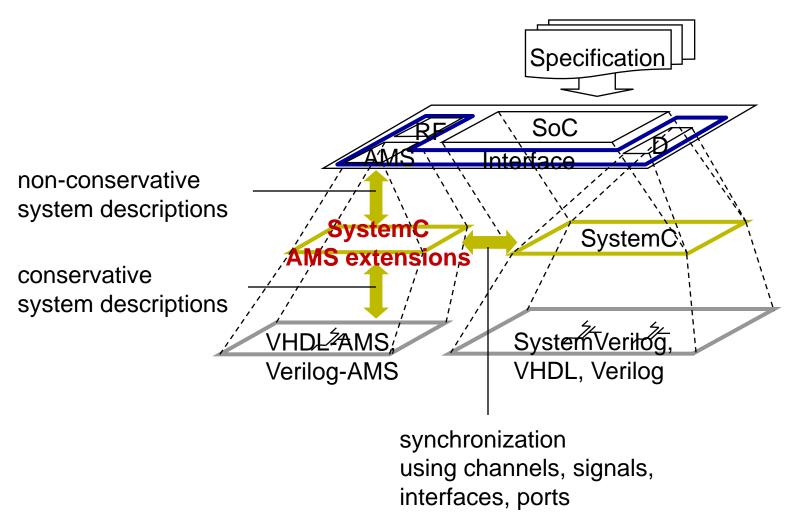

### Gap at architecture level

### Wireless ultra-low power sensor networks

#### Introduction

Design challenges and architecture gap

### OSCI SystemC AMS extensions

- use cases

- Ianguage

- Methods & support for design of sensor networks

## Current OSCI AMS WG Roster

- ESLX 🥑 SpringSoft

- Steady growth in AMS WG: 44 individuals from 19 organizations

- strong drive from semiconductor industry

- full support of universities and research institutes

- growing interest and participation of EDA/ESL vendors

- Chair: Martin Barnasconi, NXP Semiconductors

Vice chair: Christoph Grimm, Vienna University of Technology

# OSCI AMS Working Group scope

- Embedded analog/ mixed-signal systems

- Heterogeneous systems including analog, mixedsignal, RF and digital HW/SW

- Targeted application domains

- Wireless

- Wired

- Automotive

- Imaging sensors

| End Product Markets  | 2003  | 2004  | 2005  | 2006  | 2007                 |

|----------------------|-------|-------|-------|-------|----------------------|

| Microprocessor/DSP   | 18.9% | 16.0% | 13.1% | 10.5% | 14.7%                |

| Computer, Peripheral | 22.9% | 21.6% | 18.5% | 24.2% | 19.0%                |

| Wired Network        | 11.2% | 5.2%  | 5.8%  | 4.8%  | 5.2%                 |

| Wireless Network     | 13.1% | 10.4% | 13.1% | 7.3%  | 6.9%                 |

| Multimedia           | 25.6% | 34.2% | 33.8% | 37.9% | 31.9%                |

| Automotive           | 1.9%  | 3.0%  | 3.8%  | 4.0%  | 4.3%                 |

| Others               | 6.4%  | 9.7%  | 11.9% | 11.3% | 18 <mark>.</mark> 1% |

source: SystemC Trends report, April 2007

focus of AMS WG

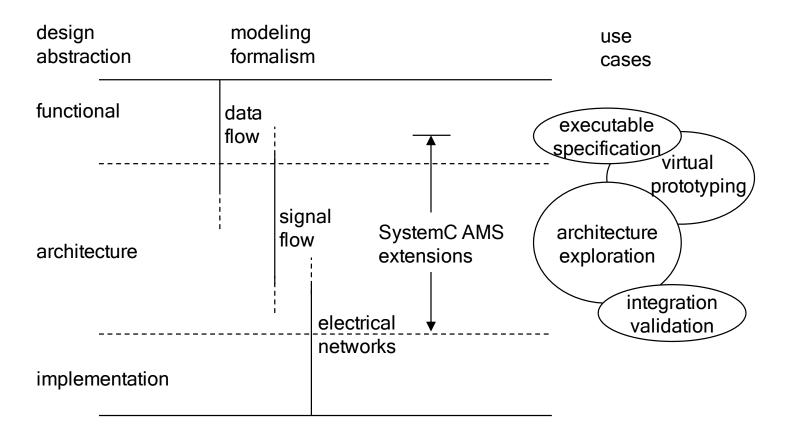

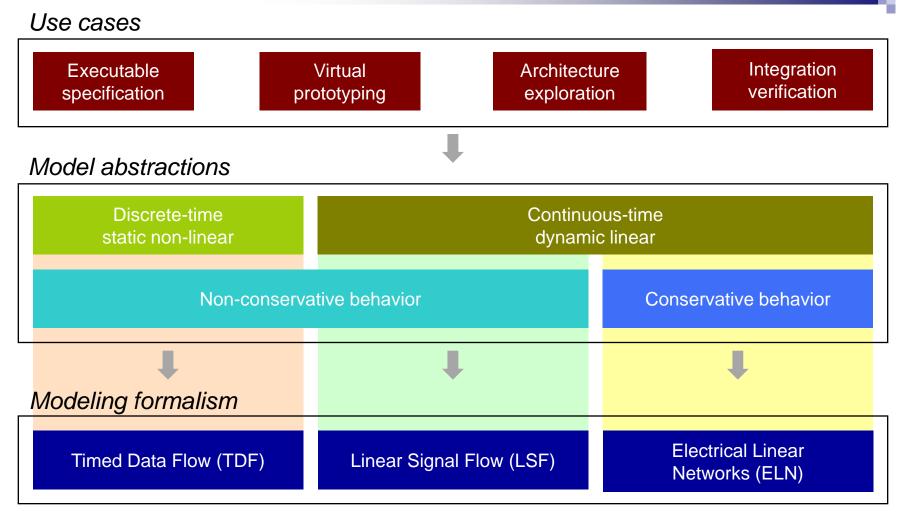

## Between functional model and implementation

[Grimm/Barnasconi/Vachoux/Einwich: An Introduction to Modeling Embedded Analog/Mixed-Signal Systems using SystemC AMS Extensions. OSCI, June 2008]

## Use case: executable specification

- Objective: verify the system specification by creating a executable description of the system using simulation

- Highest level of design abstraction applied, using functional models and signal processing algorithms

- Timed Data Flow and Linear Signal Flow modeling formalisms used

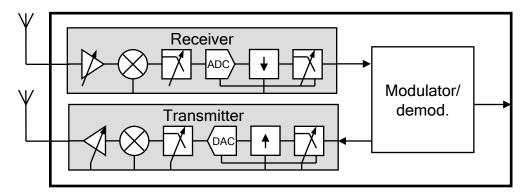

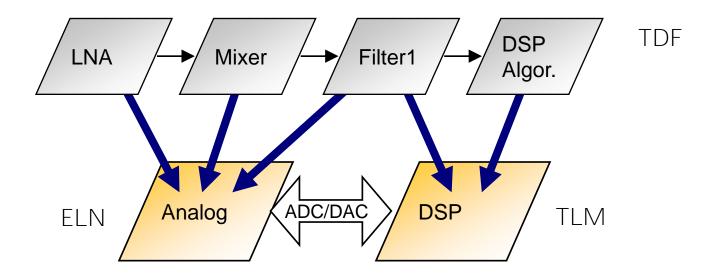

Transceiver based on functional models

## Use case: architecture exploration

- Objective: determine, evaluate and dimension the key properties of the system architecture

- Two phases

- Refinement of executable specification by adding non-ideal properties

- Introduce interfaces components and architectural elements to match the final implementation

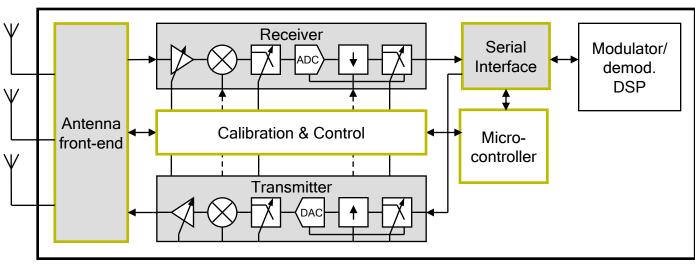

Transceiver including architecture elements (MCU, serial interface, ...)

## Use case: integration validation

Objective: accurate modeling of interfaces of all subsystems

- analog circuits/subsystems: introduce electrical nodes

- digital circuits/subsystems: bit/cycle accurate signals and busses

- HW/SW subsystem (CPU, MCU): TLM interfaces

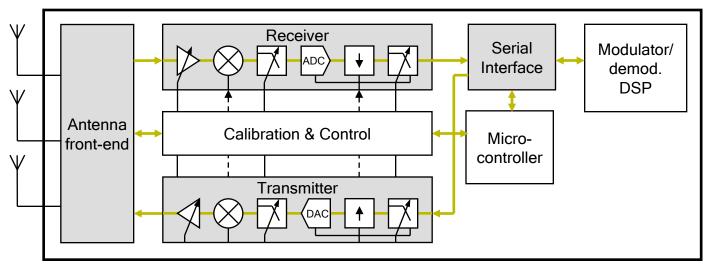

Transceiver subsystems modeled with accurate interfaces

## Use case: virtual prototyping

- Objective: SW development using a high-level untimed or timed model that represents the AMS sub-system

- Interoperability with SystemC TLM extensions expected

- Modeling formalism used: Timed Data Flow, incorporating untimed models if needed

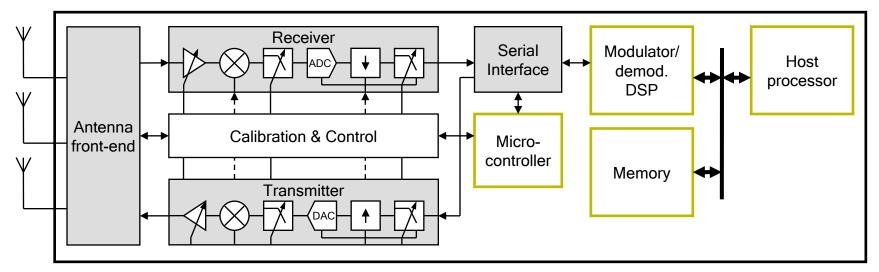

Transceiver subsystem connected to digital virtual platform

## Model abstraction and formalisms

SystemC AMS extensions

| SystemC<br>methodology-                                  | AMS methodology-specific elements<br>elements for AMS design refinement, etc. |                                                            |                                                         |                                                               |  |  |

|----------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------|--|--|

| specific<br>elements<br>Transaction<br>Level<br>Modeling | Electrical Linear<br>Networks (ELN)<br>modules<br>terminals<br>nodes          | Linear Signal<br>Flow (LSF)<br>modules<br>ports<br>signals | Timed Data<br>Flow (TDF)<br>modules<br>ports<br>signals | User-defined<br>AMS extensions<br>modules<br>ports<br>signals |  |  |

| Cycle/bit<br>Accurate<br>Modeling                        | Linear DAE solver                                                             |                                                            | Scheduler                                               | (e.g. additional<br>solvers/<br>simulators)                   |  |  |

| etc.                                                     | Synchronization                                                               |                                                            |                                                         |                                                               |  |  |

| SystemC Language Standard                                |                                                                               |                                                            |                                                         |                                                               |  |  |

C. Grimm - Design Refinement for Wirless Sensor Networks

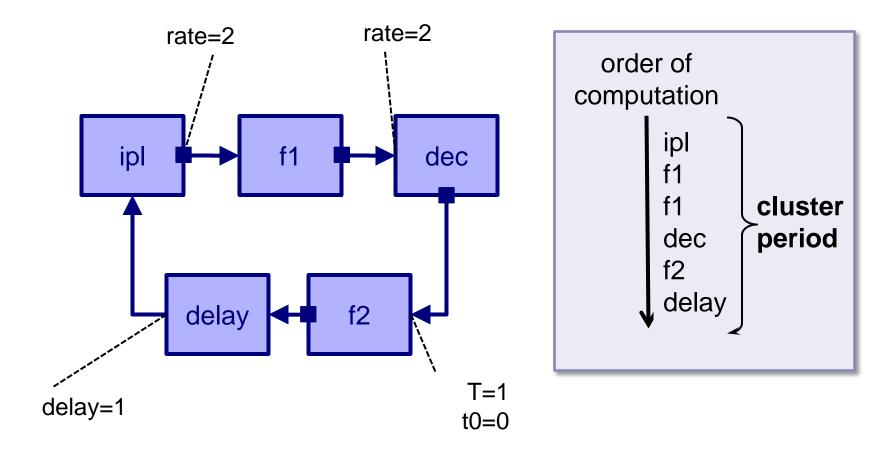

## Timed Data Flow

#### "cluster" := set of connected TDF modules

## Timed Data Flow: Serializer Example

| TDF Module:<br>primitive module!         | <pre>SCA_TDF_MODULE(par2ser) {     sca_tdf::sca_in<sc_bv<8> &gt; in;     sca_tdf::sca_out<bool> out;</bool></sc_bv<8></pre>     |  |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| Attributes specify timed semantics       | <pre>void set_attributes() { out.set_rate(8);    out.set_delay(1);    out.set_timestep(1, SC_MS);}</pre>                        |  |

| processing()<br>describes<br>computation | <pre>void processing() {    for (int i=7; i &gt;= 0 ; i )       out.write(in.get_bit(i), i);    }    SCA_CTOR(par2ser); }</pre> |  |

WIEN

## Timed Data Flow: Connecting to SystemC

Converter ports towards discrete event domain

sca\_tdf::sc\_in < <type> >

sca\_tdf::sc\_out < <type> >

Note: Time in MR – TDF may sc\_time sca\_get\_time() run ahead DE time!

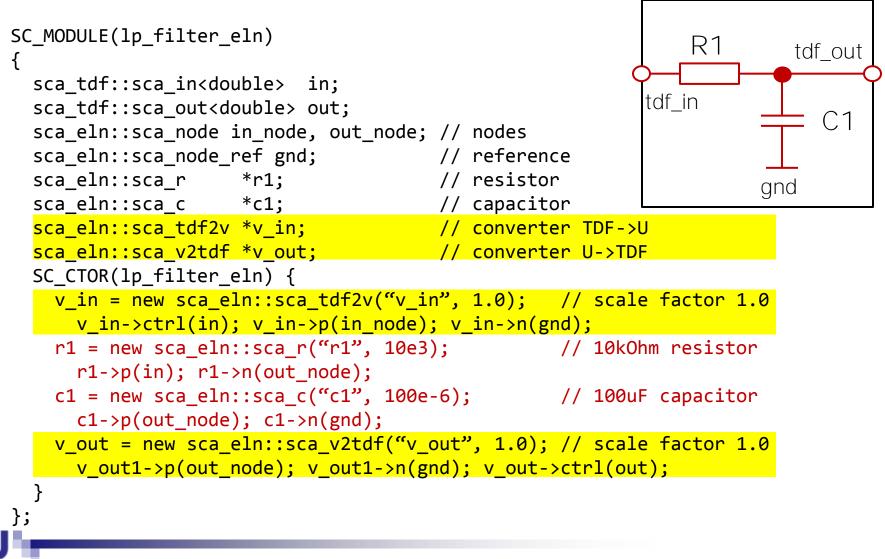

Linear Electrical Networks

### Wireless ultra-low power sensor networks

#### Introduction

- Design challenges and architecture gap

- OSCI SystemC AMS extensions

- Support for refinement of sensor networks

- 1. Methodology

- 2. Methodology specific support

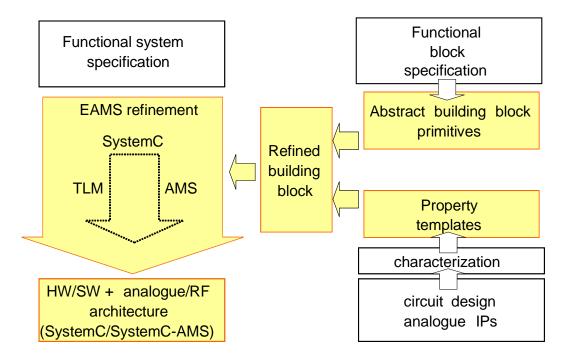

## "Design Refinement" methodology

Remember the challenge: Design at architecture level, considering abstract overall-system (e.g. network protocols, ...) and at the same time circuit level properties in some parts in a top-down methodology.

## "Design Refinement" methodology

**Design Refinement** is a top-down methodology that successively augments and integrates properties of an implementation into a functional model, and analyzes their impact.

- Related, but not the same:

- Extreme programming (SW engineering method)

- Property refinement (Formal method, maintains safety properties)

## Design refinement - classification

- Functional level (starting point)

- Architecture level

- Refinement of computation -> Computation accurate model Algorithms, data types, physical effects/accuracy

- Refinement of structure -> Structure accurate model Mapping to processors or functional blocks

- Refinement of interfaces -> Interface accurate model Signals, synchronization, bus protocols

- Implementation

**Objective:** Evaluate impact of non-ideal behavior of an assumed architecture to overall functionality (e.g. performance figures). **Method:**

- Add non-ideal effects to executable, *functional* spec

- non-ideal behavior can be written directly in C-code!

```

void processing() // Mixer refined with distortions and noise

{

double rf = in1.read();

double lo = in2.read();

double rf_dist = (alpha - gamma * rf * rf ) * rf;

double mix_dist = rf_dist * lo;

if_out.write( mix_dist + my_noise() );

}

```

## Refinement of structure, re-partitioning

Objective: Compare performance of different A/D/HW/SW partitionings more accurately.

Map functions of specification to processors, adapt structure of functional spec to architecture structure.

### Refinement of structure, re-partitioning

#### Method 1:

Re-write functional part that is re-partitioned in new model of computation that matches intended realization (cumbersome ...)

- Analog: Signal flow, Network

- Digital HW: TDF, DE ( or TLM)

- Slightly simplified by "static polymorphism"

```

SCA_MOC_MODULE(par2ser)

{

sca_MoC::sca_in<sc_bv<8> > in;

sca_MoC::sca_out<bool> out;

...

SCA_CTOR(par2ser)

}

```

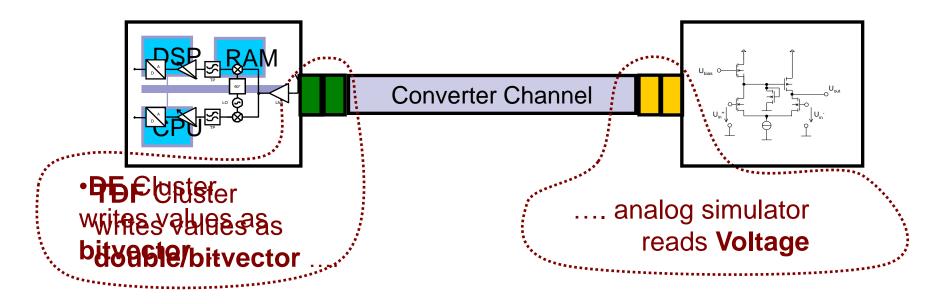

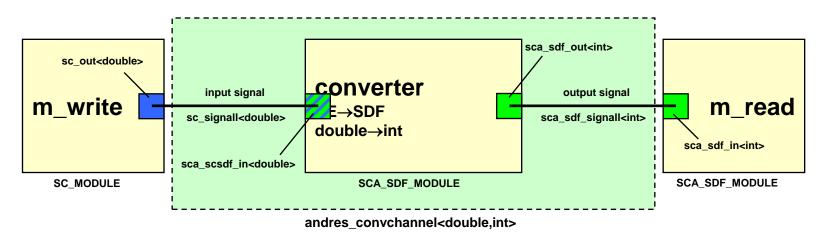

### Refinement of structure, re-partitioning

#### Method 2:

Bottom-up integration of available models (e.g. library)

**"Converter channel"** is hierarchical channel that separates modeling artefacts to translate MoC from "real" design.

Intention: Used for verification of system integration

All ports accurately as in implementation (same types, same number, clocks, enable-signals, ...)

#### Method 1:

Use adapter classes that translate between abstract data flow and pin-accurate protocols or analog nodes (requires appropriate models inside)

#### • Method 2:

Clock signals or events determine activation of TDF cluster (allows combination of functional TDF description with complex control signals for validation of control signals)

### Design methodology specific library

Application domain: Design refinement of *communication* systems and sensor networks.

Components:

- Signal sources

- Converters

- Mappers / Demappers

- Modulators / Demodulators

- Misc (e.g. FFT, ...)

- Analysis tools

... and more: Support for design refinement - Converter channels - Adapter classes

- All modules highly configurable

#### Binary Amplitude Shift Keeying Modulator

#### Class definition: andres\_bb\_mod\_bask(sc\_module\_name nm, double \_freq, double \_ampl1, double \_ampl0, double \_phi, int \_rate); Interfaces: sca\_sdf\_in<bool> in; sca\_sdf\_out<double> out;

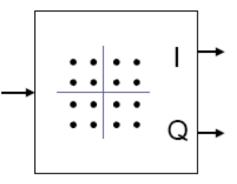

#### ■ IQ mapper (4,16, 64, ...)

#### Class definition: andres\_bb\_mod\_iq(sc\_module\_name nm, double \_freq, double \_d\_ampl, double \_d\_phi, int \_rate); Interfaces: sca\_sdf\_in<double> i ; sca\_sdf\_in<double> i ; sca\_sdf\_in<double> q ; sca\_sdf\_out<double> out ;

### Methodology specific support: converter channels

Converter channels specifically support the refinement of structure / re-partitioning.

Converter channel adapts

MoC, data type, sample rates

after refinement steps

C. Grimm - Design Refinement for Wirless Sensor Networks

### Coupling SystemC-AMS TDF and LT-TLM?

- SystemC-AMS is basically *strictly* timed, so connecting with *loosely* timed models seems futile...

- **but** TDF has also a kind of "time-warp".

- A source process with datarate > 1 also sends values "to the future" with respect to the current SystemC (and even SystemC-AMS!) simulation time.

- A drain process with datarate > 1, it **also receives "future values**.

- SystemC-AMS time is always ≥ SystemC time

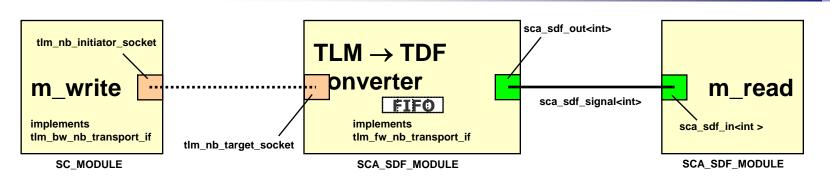

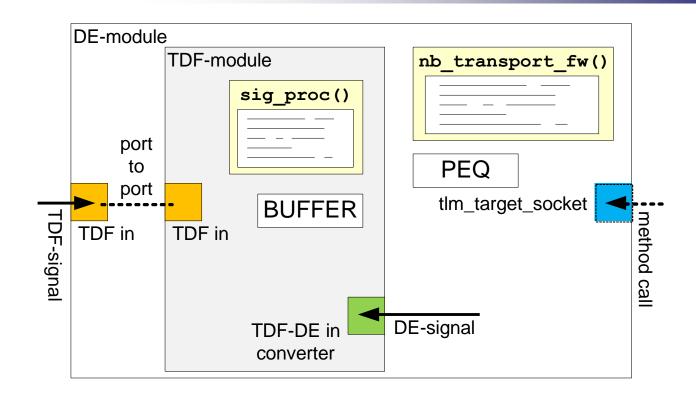

### Conversion TLM $\rightarrow$ TDF

- Basic idea: Stream the data of the input transactions to a TDF signal with datarate rt

- The transaction data are **buffered** within an internal FIFO

- At every sig\_proc() execution, rt many values are taken from the buffer and written to the TDF output port

- Empty buffer  $\Rightarrow$  send default values or throw error / warning

- If a transaction causes a buffer overflow we return the transaction with a TLM\_GENERIC\_ERROR\_RESPONSE

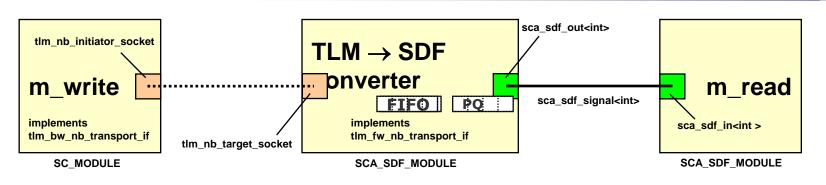

### Conversion TLM $\rightarrow$ TDF

- Problems:

- The transactions may arrive out of order with respect to their time stamps.

- ⇒ We use a payload event queue (PEQ) to store the transactions before writing their data to the buffer, which we only do when necessary (i.e. when the buffer has less data than the datarate).

- The PEQ sorts the transactions according to their time stamp.

- the data from a transaction is written into the buffer as late as possible.

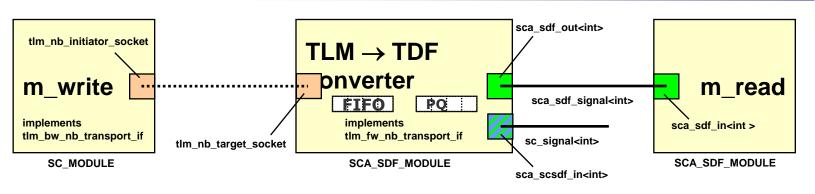

### Conversion TLM $\rightarrow$ TDF

- ...more problems:

- The converter may run ahead so far that the initiators might not had the chance to produce sufficient transactions to fill the buffer (even though they would).

- $\Rightarrow$  We have to trigger t<sub>DE</sub>-t<sub>TDF</sub> synchronization.

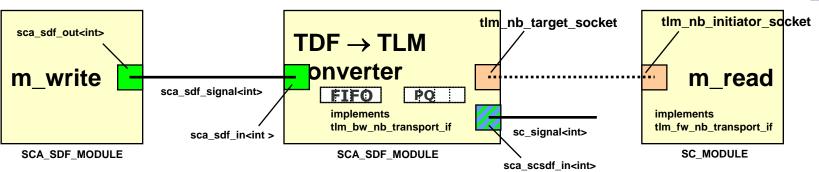

## Conversion TDF $\rightarrow$ TLM

- **Basic idea:** Bundle the streaming data from the TDF side into transactions.

- The TLM side sends read transactions (requests) to the converter, who copies the requested data into the transaction and returns it.

- We use an internal buffer and PEQ again

- t<sub>DE</sub>-t<sub>TDF</sub> synchronization needs due to full internal buffer. Access to internal converter port gives the TLM side a chance to produce sufficient *read* transactions.

- Still buffer overflow? ⇒ data loss or error/warning

### $TDF \rightarrow TLM$ converter architecture

#### • Basically pretty similar to the TLM $\rightarrow$ TDF converter.

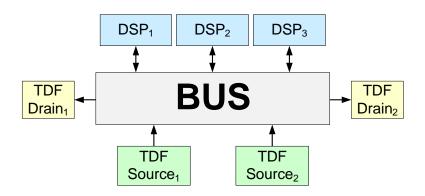

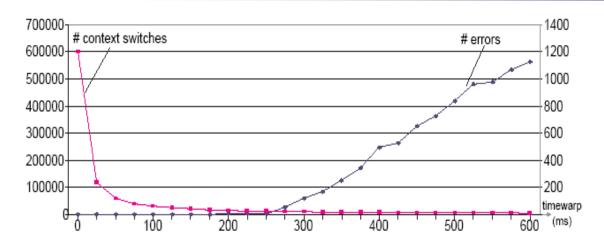

### Experimental results

- Toy example: Three DSPs access two TDF drains and two TDF sources via a bus concurrently.

- If a DSP read from source 1 (source 2), it processes the data and writes the results to drain 1 (drain 2).

- Possible scenario: Software Defined Radio. Two different modulation schemes are used.

- Goal here: Testing functional correctness, observing simulation speed / simulation accuracy trade-offs.

### Experimental results

- We took the number of context switches (of the DSPs) as a measure for the simulation performance.

- The Arrival of an data packet in the wrong order constitutes as an error.

- About 12000 data packets were processed by the system

Tools to analyze signal quality by plotting

eye diagrams

trellis diagrams

constellation diagrams

... as SVG file

### Analysis tools: Power metering

- Consumers

- HW moule usage

- CPU usage

- Power consumption/use by

- circuit-level simulation

- measurement

- data sheets

- Usage profile collected in log fil

- Post Processing

- Analysis

- Visualization

| diama              |                                | Data Processing: log2.lot                 |

|--------------------|--------------------------------|-------------------------------------------|

| Fig Atast          |                                |                                           |

| 800.000            |                                |                                           |

|                    |                                |                                           |

| 800.008            |                                |                                           |

|                    |                                |                                           |

| 703.038            |                                |                                           |

|                    |                                |                                           |

| 600.022            |                                | 8314 128ms                                |

|                    |                                | Physics 74 430 m dV<br>result 17 130 m dV |

|                    |                                | gtoball 0.020mW                           |

|                    |                                | 103.385m.W                                |

|                    | 338.2                          | 46mW                                      |

|                    |                                |                                           |

|                    |                                |                                           |

| 20.0 .00           |                                |                                           |

|                    |                                |                                           |

| 100.000            |                                |                                           |

|                    |                                |                                           |

| 1.045              |                                |                                           |

|                    |                                |                                           |

|                    |                                |                                           |

| 200.000            |                                |                                           |

|                    |                                |                                           |

| Data               |                                |                                           |

| gistal 🔅           | Relaat TX Key                  |                                           |

| - Data Rows:       |                                |                                           |

|                    |                                |                                           |

|                    | Integrate Providue             |                                           |

| - Starphy<br>Types |                                |                                           |

| 3                  |                                |                                           |

| La render          | Integrate All 🖌 Group to great |                                           |

|                    |                                |                                           |

|                    |                                |                                           |

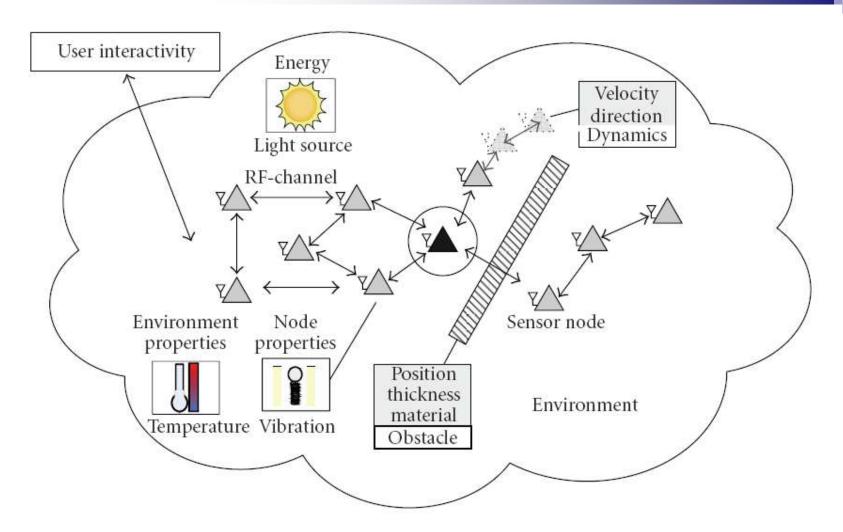

#### Simulation scenario

#### Dynamic scenarios

### Library object "air"

- Global "Air" object

- Acts like a Switch

- Considers 3D arrangement, Obstacles

- Attenuation, distortion, noise

- Every node connects to it

- "RF Messages" are distributed

- Use BB equivalent instead of real RF

- First version: PAWIS project, ongoing work in SNOPS project.

#### Wireless ultra-low power sensor networks

#### Introduction

- Design challenges and architecture gap

- OSCI SystemC AMS extensions

- Support for refinement of sensor networks

- SystemC AMS is gaining impact for architecture-level design of complex heterogeneous systems

- Well applicable for E-AMS systems, where HW/SW and AMS are functionally interwoven

- Design refinement modeling strategy integrates architecture properties successively into functional model

- Quickly available first models

=> Early feedback on feasibility or potential issues

- Immediate analysis/verification after changing/adding property => Optimization / debugging more efficient

- www.systemc.org, AMS WG (OSCI members)

- <u>www.systemc-ams.org</u> (For information from former SystemC-AMS SG, provides some information for the public)

- Ch. Grimm, M. Barnasconi, A. Vachoux, K. Einwich: An Introduction to Modeling Embedded Analog/Mixed-Signal Systems using SystemC AMS Extensions. OSCI, June 2008

- Ch. Grimm: Modeling and Refinement of Mixed Signal Systems with SystemC. In: SystemC: Methodologies and Applications. Kluwer Academic Publisher (KAP), June 2003.

- Johann Glaser, Daniel Weber, Sajjad A.Madani, and Stefan Mahlknecht: Power Aware Simulation Framework for Wireless Sensor Networks and Nodes. In: Ch. Grimm (editor) EURASIP Journal on Embedded Systems; Special issue on C-Based Design of Heterogeneous Systems; vol. 2008, Article ID 369178.

# Thank you for your attention!

- Your:

- questions

- comments

- ideas

- objections