## Silicon-based RF ICs up to 100 GHz: Research Trends and Applications

W. Simbürger<sup>1</sup>, K. Aufinger<sup>1</sup>, J. Böck<sup>1</sup>, S. Boguth<sup>1</sup>, D. Kehrer<sup>1</sup>,

C. Kienmayer<sup>1,3</sup>, H. Knapp<sup>1</sup>, T.F. Meister<sup>1</sup>, W. Perndl<sup>1,3</sup>, M. Rest<sup>1</sup>,

C. Sandner<sup>2</sup>, H. Schäfer<sup>1</sup>, R. Schreiter<sup>1</sup>, R. Stengl<sup>1</sup>, R. Thüringer<sup>1,3</sup>,

M. Tiebout<sup>1</sup>, H.D. Wohlmuth<sup>1</sup>, M. Wurzer<sup>1</sup> and A.L. Scholtz<sup>3</sup>

<sup>1</sup>Infineon Technologies AG, Otto-Hahn-Ring 6, D-81739 Munich, Germany <sup>2</sup>Infineon Technologies AG, Siemensstrasse 2, A-9500 Villach, Austria <sup>3</sup>Vienna University of Technology, Gusshausstr. 25/389, A-1040 Vienna, Austria

Email: werner.simbuerger@infineon.com

#### **Abstract**

This paper presents recent advances in circuit design which evaluate the high-speed and low-power potential of state-of-the-art CMOS and SiGe bipolar technologies.

In 0.13  $\mu$ m CMOS a 17 GHz ISM/WLAN RF front-end with only 130 mW power consumption is described. An injection locked frequency divider with a power consumption as low as 3 mW at 40 GHz is presented. A fully integrated 2:1 multiplexer IC which operates up to 50 Gb/s data rate has been realized in CMOS.

A 100 Gbit/s amplifier in a 200 GHz/275 GHz  $f_T/f_{max}$  SiGe bipolar technology with 16 dB gain has been realized. Finally, a 65 GHz - 95 GHz double-balanced mixer for 77 GHz automotive radar applications is discussed.

### 1 Introduction

Current indium phosphide (InP) bipolar integrated-circuits support high-performance mixed-signal applications at frequencies up to 200 GHz and beyond [1, 2]. The high cut-off frequencies and high breakdown voltages present a unique combination which addresses some major issues. In the meantime, silicon bipolar and CMOS technologies are not standing still. Silicon germanium (SiGe) has brought substantial improvements in bipolar circuit performance [3, 4, 5, 6, 7]. Recently, CMOS is capturing a significant portion of wireless RF and wireline applications with the promise of lower costs and increased integration scale at highest frequencies [8, 9, 10, 11].

This work summarizes recent circuit results in 0.13  $\mu m$  standard bulk-CMOS and in a productionnear 200 GHz/275 GHz  $f_T/f_{max}$  SiGe bipolar technology.

### 2 A 17 GHz ISM/WLAN RF frontend with only 130 mW power consumption in 0.13 $\mu$ m CMOS

With growing interest in broadband wireless communication systems and faster and high-performance transceivers at data rates of 100 Mbit/s to 1 Gbit/s and beyond, submicron CMOS is particularly attractive for RF and digital baseband processing because of its low power consumption and high integration scale. Emerging short-range applications, such as a high-speed wireless USB 2.0 interface for example, will rely on a low power consumption for mobile systems.

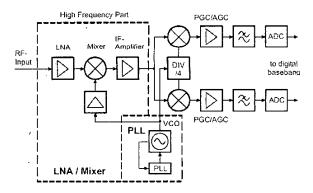

Figure 1: 17 GHz ISM/WLAN RF frontend block diagram [12, 13].

Fig. 1 shows the block diagram of an integrated RF frontend for 17.1-17.3 GHz ISM band application. The high frequency part of the RF transceiver consists of a LNA and mixer [12] and a high-performance PLL [13]. The concept of the dual conversion (Fig. 1) results in a large

0-7803-8511-X/04/\$20,00 ©2004 IEEE.

frequency separation between the RF and LO frequencies and avoids the generation of I/Q signals at the first LO frequency.

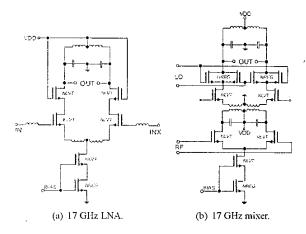

LNA and mixer design is one of the main challenges, since this circuit determines the total gain, noise figure and linearity performance of a receiver. Fig. 2 shows a simplified schematic diagram of the 17 GHz LNA and mixer in 0.13  $\mu m$  CMOS.

Figure 2: 17 GHz LNA / mixer schematic diagram [12].

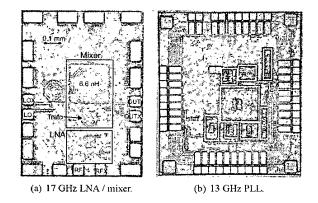

The LNA core in Fig. 2(a) consists of a cascoded, inductively degenerated common source input stage. Inductive degeneration is employed at the common source node of the LNA to achieve a real valued input impedance and low noise figure. The LNA-output is loaded by an integrated LC-tank to increase the gain. Due to the high frequency of 17 GHz all inductors can nicely be integrated without significant area penalty (see chip photograph Fig. 3(a)). A simplified schematic diagram of the mixer is shown in Fig. 2(b). The classical Gilbert-type mixer was preferred to achieve acceptable gain, low noise figure and high linearity. To overcome problems caused by the low supply voltage of 1.5 V in 0.13  $\mu$ m CMOS, a fully differential integrated transformer was connected between the input transconductance stage and the mixer switching pairs. This topology effectively doubles the voltage headroom available for the circuit design and enables the insertion of cascode transistors to improve the linearity and to control the current in the mixer switching stage. Fig. 3(a) shows the chip photograph of the LNA / mixer. The block diagram of the LNA / mixer is shown in Fig. 1.

In Tab. 1 the measured performance of the 17 GHz LNA / mixer is summarized.

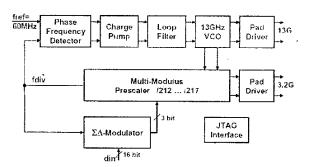

The block diagram of the PLL is shown in Fig. 4. The PLL is completely integrated including VCO, prescaler, phase frequency detector, charge pump, loop filter, biasing, delta-sigma modulator and a JTAG controller [13]. The PLL uses a multi-modulus prescaler with a division rate of 212...217 to allow effective fractional-N synthesis and delta-sigma modulation. Aiming at a fully integrated

Figure 3: 17 GHz LNA mixer and 13 GHz PLL chip photograph [12, 13].

Table 1: 17 GHz LNA / mixer measurement results [12].

| Power supply                   | 1.5 V                     |

|--------------------------------|---------------------------|

| Total power consumption        | 70 mW                     |

| LNA power consumption          | 5.2 mW                    |

| Mixer power consumption        | 27 mW                     |

| LO-Driver power consumption    | 12 mW                     |

| IF-Amplifier power consumption | 25.8 mW                   |

| IF frequency                   | 3.4 GHz                   |

| LO frequency                   | 13.95 GHz                 |

| RF frequency                   | 17.35 GHz                 |

| Power gain                     | 34.7 dB                   |

| Noise figure SSB               | 6.6 dB                    |

| CP <sub>1dB</sub> (input)      | -39 dBm                   |

| IIP3                           | -34.4 dBm                 |

| 3 dB bandwidth                 | 200 MHz                   |

| Testchip die area              | $0.88 \text{ mm}^2$       |

| Technology                     | $0.13~\mu\mathrm{m}$ CMOS |

Figure 4: 13 GHz PLL block diagram [13].

high performance 17 GHz transceiver including LNA and output driver, special care was invested to avoid substrate crosstalk, so a differentially tuned LC-VCO was implemented.

| Table 2: I | 3 GHz PLL | measurement results | [13]. |

|------------|-----------|---------------------|-------|

|------------|-----------|---------------------|-------|

| Center frequency              | 13 GHz                    |

|-------------------------------|---------------------------|

| VCO tuning range              | 8 %                       |

| Reference frequency           | 60 MHz                    |

|                               | (64 MHz for N=200)        |

| Inband phase noise (@ fvco/4) | -100 dBc/Hz               |

| RMS Phase error (@ fvco/4)    | 1.6 deg (N=214.5044)      |

| (10kHz to 100MHz)             | 3.0 deg (N=214.992)       |

| Power supply                  | 1.5 V                     |

| Total Power consumption       | 60 mW                     |

| VCO                           | 5 mW                      |

| Div/4                         | 40 mW                     |

| Prescaler                     | 1 mW                      |

| Loop Filter                   | 5, mW                     |

| Charge pump                   | 3 mW                      |

| Others, incl. digital         | 6 mW                      |

| Testchip die area             | 1.8 mm by 1.6 mm          |

| Technology                    | $0.13~\mu\mathrm{m}$ CMOS |

In Tab. 2 the performance of the PLL is summarized [13]. The total power consumption of LNA / mixer and PLL is only 130 mW in 0.13  $\mu m$  CMOS at 17 GHz.

# 3 40 GHz, 3 mW low-power injection locked frequency divider in 0.13 $\mu$ m CMOS

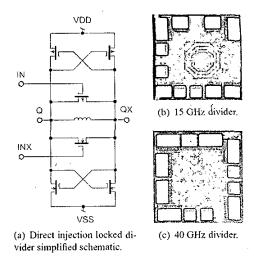

RF Phase locked loops are widely used in wireless and wireline applications as frequency synthesizers or clock sources. Crucial high frequency PLL-components are the voltage controlled oscillator (VCO) and the high frequency dividers. Main concern for VCO-design is low phase noise and low power consumption. Main concern for the frequency divider is lowest power consumption and high frequency capability. High frequency dividers can be realized using CML-logic, using dynamic logic, using a Miller divider or through the injection locking of oscillators. Miller-dividers and CML dividers have been realized up to very high frequencies, unfortunately with high or very high power consumption. Dynamic logic frequency dividers feature a very small power consumption, but the maximum frequency of operation is limited to a few GHz. Injection locked oscillators consume generally less power than CML- or Miller-dividers due to the tuned nature of the circuit. One disadvantage of injection locked oscillators is the limited input bandwidth (or input locking range), which fortunately is not very relevant in LC-VCO based PLL's, as LC-VCO's anyway feature a limited tuning range. The main disadvantage of today's widely used CMOS differential injection locked oscillator topology is found in the large input capacitance and in its small input locking range. A CMOS low power direct injection lock-

Figure 5: Direct injection locked divider simplified schematic diagram. 15 GHz and 40 GHz injection locked divider chip photograph [14].

ing scheme [14] for LC-oscillators is presented in Fig. 5 to divide highest frequency signals with lowest input capacitance.

The proposed topology consists of MOS-switches directly coupled to the tank. The concept is verified with two fully integrated injection locked oscillators aiming at different frequencies. The measured frequency locking characteristics and phase noise clearly verifies the circuit implementation. A CMOS low power injection locked oscillator performs highest frequency division by two consuming only 3 mW from 1.5 V supply voltage. The measured circuit divides 41 GHz by two with a locking range of 1.5 GHz. A second oscillator aiming at 15 GHz features a total locking range of 14.2-17 GHz at a power consumption of 23 mW. The increased locking-range of this divider results in increased power consumption [14]. The measurement results are summarized in Tab. 3.

Table 3: Injection locked divider performance [14].

| Technology        | 0.13 μm CMOS  |               |

|-------------------|---------------|---------------|

| Supply voltage    | 1.5           | ίV            |

| Power Consumption | 3 mW          | 23 mW         |

| Locking Range     | 40.5 - 42 GHz | 14.2 - 17 GHz |

# 4 A 50 Gb/s 2:1 Multiplexer in 0.13 $\mu$ m CMOS

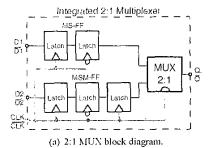

Data multiplexers (MUX) are key blocks in high-speed data communication systems. Current 2:1 MUX already achieve operating speeds of 50 Gb/s in 90 nm CMOS [10]. A fully integrated 2:1 multiplexer IC which also operates

(b) 2:1 MUX core schematic diagram.

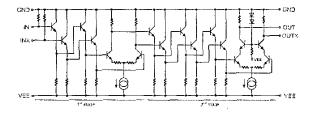

Figure 6: 50 Gb/s 2:1 MUX in 0.13  $\mu$ m CMOS: block diagram and MUX core schematic diagram [15].

at 50 Gb/s data rate has been realized in standard 0.13  $\mu$ m bulk-CMOS technology [15].

Fig. 6 shows the block diagram and the schematic diagram of the core multiplexer circuit. The 2:1 MUX IC consists of a master-slave flip-flop (MS-FF), a master-slave-master flip-flop (MSM-FF) and a multiplexer stage (MUX 2:1). The MUX stage uses series gating between clock and data input. All transistors in the MUX stage data path are of the same size and are 3/5 the width of the clock transistors. The MUX stage uses 70 \Omega poly-silicon load resistors which is a compromise between high voltage swing and reasonable output matching. The tail current is set to 7 mA. To enhance the operating bandwidth of the multiplexer, inductive shunt peaking and series peaking is used. The output network acts as a filter which consists of various parasitic capacitances, load resistors, bond inductances and on-chip inductors  $L_p$  and  $L_s$ . The inductor  $L_s$  is in series to the output and needs therefore a high Qfactor while the Q-factor of the inductor  $L_p$  is determined by the load resistors  $R_L$ . To reduce capacitance to substrate only the top metal is used. The spacing between the turns is kept wide to reduce turn-to-turn parasitic capacitance.

For measurement the 2:1 MUX IC is bonded on a Rogers RO4003 microwave substrate. The multiplexer is tested with two pseudo-random bit sequences (PRBS of  $2^7$ -1). The input voltage swing is 2 x 500 mV<sub>pp</sub>. The sinusoidal

(a) Chip photograph.

(b) 50 Gb/s measured eye diagram.

Figure 7: 50 Gb/s 2:1 MUX in 0.13  $\mu$ m CMOS: chip photograph and measured eye diagram [15].

clock signal has a voltage swing of 2 x  $400~\text{mV}_{pp}$ . Fig. 7 shows the measured eye diagram of the differential output signal at a data rate of 50 Gb/s. Tab. 4 shows the performance summary of the MUX.

Table 4: 50 Gb/s 2:1 MUX measurement results [15].

| Power supply                        | 1.5 V                          |

|-------------------------------------|--------------------------------|

| Total power consumption             | 98 mW                          |

| Maximum data rate                   | 50 Gb/s                        |

| Output voltage swing (50 $\Omega$ ) | $2 \times 100 \text{ mV}_{pp}$ |

| Testchip die area                   | 0.63 mm by 0.47 mm             |

| Technology                          | 0.13 μm CMOS                   |

# 5 A 100 Gbit/s amplifier in SiGe bipolar technology

A broadband amplifier with 16 dB gain and a 3-dB bandwidth of 62 GHz has been realized in a 200 GHz  $f_T$ , 275 GHz  $f_{max}$  SiGe bipolar technology [16, 17]. Broadband amplifiers are very important building blocks for a large variety of applications, including wireless transceivers, num-wave applications and optical communication systems. In general, they are based on a lumped [18, 19, 20] or on a distributed concept [21, 22, 18].

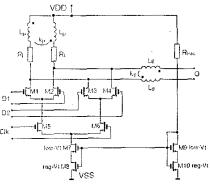

The circuit diagram of the broadband amplifier based on

Figure 8: 62 GHz, 16 dB gain broadband amplifier schematic diagram [16].

lumped elements realized in this work is shown in Fig. 8. The amplifier is based on a fully differential design and consists of two stages.  $50\,\Omega$  on-chip resistors are provided at the input and the output for broadband matching. In addition, emitter degeneration and low load resistors are used for increasing the 3-dB bandwidth at a well-defined gain. Carefully adjusted transistor sizes and currents enable a flat transfer function and a high bandwidth. The differential amplifier of the second stage is implemented as cascode configuration in order to prohibit avalanche breakdown of the output transistors. The cascode stage additionally minimizes the Miller effect, thereby bandwidth is increased.

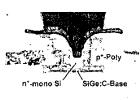

(a) Amplifier chip photograph.

(b) SiGe BJT TEM cross section.

Figure 9: Chip photograph of the 62 GHz, 16 dB gain broadband amplifier in SiGe (chip size:  $550 \,\mu\text{m} \times 550 \,\mu\text{m}$ ) [16] and TEM cross section of the emitter-base complex of a SiGe transistor with effective emitter width of  $0.14 \,\mu\text{m}$  [17].

The chip photograph of the amplifier is shown in Fig. 9(a). The amplifier is fabricated in a preproduction SiGe bipolar technology [17]. The transistors have a doublepolysilicon self-aligned emitter-base configuration with a minimum effective emitter width of  $0.14 \,\mu\text{m}$ . A TEM cross section of the emitter-base complex is given in Fig. 9(b). The SiGe:C base of the transistors has been integrated by selective epitaxial growth. The emitter contact exhibits a monocrystalline structure. The transistors manufactured in this technology offer a transit frequency f<sub>T</sub> of 200 GHz, a maximum oscillation frequency f<sub>max</sub> of 275 GHz and a ring oscillator gate delay of 3.5 ps. Current density for maximum  $f_T$  and  $f_{max}$  is at about 8 mA/ $\mu$ m<sup>2</sup>. The collector-emitter breakdown voltage BV<sub>CE0</sub> is 1.7 V. The technology provides four copper metallization layers, two different types of polysilicon resistors, a TaN thin film resistor and a MIM capacitor.

The single-ended low-frequency gain is  $10 \, dB$  and the 3-dB bandwidth is  $62 \, GHz$ . The differential gain is  $16 \, dB$ . The current consumption is  $155 \, mA$  at a supply voltage of -5 V. Degradation of  $S_{22}$  at about  $50 \, GHz$  can be observed. In the case of a single-ended excitation together with an inductance in the supply path this behavior can be verified by simulations. In differential operation such an inductance will have no effect.

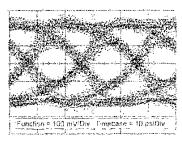

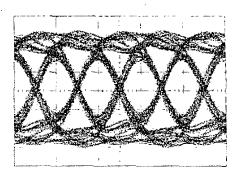

Figure 10: 100 Gb/s (250 mV/div, 5 ps/div) [16].

Table 5: Broadband amplifier measurement results [16].

| SiGe bipolar technology,  | 200/275 GHz f <sub>T</sub> /f <sub>max</sub> |

|---------------------------|----------------------------------------------|

| min. eff. emitter width,  | $0.14~\mu\mathrm{m}$                         |

| ring osc. gate delay      | 3.5 ps                                       |

| Bandwidth (3 dB)          | 62 GHz                                       |

| Differential gain         | 16 dB                                        |

| CP <sub>1dB</sub> (input) | -9.5 dBm                                     |

| IIP3                      | +2.1 dBm                                     |

| Supply voltage            | -5.0 V                                       |

| Supply current            | 155 mA                                       |

| Chip size                 | $550 \mu\mathrm{m} \times 550 \mu\mathrm{m}$ |

In Fig. 10 the measured output eye diagram for a 100 Gbit/s excitation signal is shown. A high-performance PRBS-generator chip [6] and the broadband amplifier chip have been mounted closely on a substrate. Short bond wires connect the outputs of the PRBS-generator and the amplifier inputs. The clear output eye diagram at a data rate of 100 Gbit/s demonstrates the feasibility for high-speed communications. Tab. 5 shows the performance summary.

### 6 A 65 GHz - 95 GHz doublebalanced mixer for automotive radar front-ends in SiGe bipolar technology

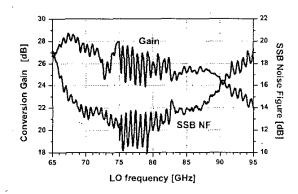

An active mixer for down-conversion with a conversion gain of more than 24 dB and single-sideband (SSB) noise figure of less than 14 dB in the frequency range from 76 GHz to 81 GHz has been realized [23]. The gain is >22 dB from 65 GHz up to 95 GHz with slightly decreased noise performance.

A simplified circuit diagram of the mixer is shown in Fig. 11. The mixer consists of a mixer core, an LO buffer, a balun at the RF input and an IF buffer. The mixer core is based on the Gilbert-mixer. The mixer has a double-balanced structure and utilizes differential LO and RF sig-

nals. Transistor sizes and bias currents are optimized in order to obtain a good compromise between gain, linearity and low noise figure. The size of the switching transistors is designed at the current density for maximum  $f_T$ , whereas the RF transistors are designed for minimum noise contribution. The differential signals required for LO and RF inputs of the mixer core are generated by the LO buffer and a LC balun, respectively. The LO buffer consists of a differential amplifier which provides a differential output signal from the single-ended input.

Figure 11: Simplified circuit diagram of the mixer (GND = 0 V, VEE = -5 V) [23].

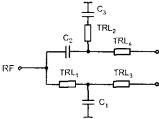

(c) Schematic diagram of the LC balun.

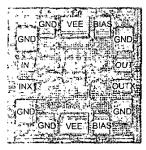

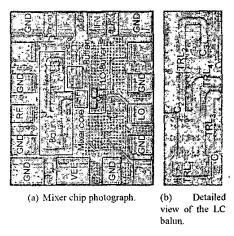

Figure 12: Chip photograph of the mixer (chip size:  $550 \,\mu\text{m} \times 450 \,\mu\text{m}$ ), detailed view of the LC balun and schematic diagram of the LC balun [23].

Fig. 12(a) shows the chip photograph of the mixer. Building blocks and important pads are indicated in the photo-

graph. The LC balun (Fig. 12(b)) is placed directly at the RF input, followed by the mixer core. The LC balun consisting of the transmission lines  $TRL_1$  and  $TRL_2$  and the MIM-capacitors  $C_1$  and  $C_2$  (Fig. 12(c)). This balun converts the unbalanced RF signal to a balanced signal and provides an impedance transformation for  $50\,\Omega$  matching at the RF input. Capacitor  $C_3$  is required to achieve an RF ground at  $TRL_2$ . The LC balun was designed based on the calculation of a lumped element balun [24]. Then the inductances were substituted with transmission line  $TRL_1$  and  $TRL_2$  [25]. Further optimization was done using an EM-field simulator.

The mixer is fabricated in a SiGe bipolar technology which is based on the process technology presented in [26]. The transistors have a double-polysilicon self-aligned emitter-base configuration with an effective emitter width of 0.18  $\mu m$ . The SiGe:C base of the transistors has been integrated by selective epitaxial growth and the transistors exhibit a monocrystalline emitter contact. The transistors manufactured in this technology offer a transit frequency  $f_{\rm T}$  and a maximum oscillation frequency  $f_{\rm max}$  of more than 200 GHz and a ring-oscillator gate delay of 3.7 ps. The technology provides four copper metallization layers, two different types of polysilicon resistors and a TaN thin film resistor.

Figure 13: Measured conversion gain and SSB noise figure versus LO frequency. IF frequency is 500 MHz, LO power is 2 dBm [23].

In Fig. 13 the measured conversion gain and SSB noise figure versus LO frequency of the mixer at a constant IF frequency of 500 MHz are shown. The LO input power is set to 2 dBm at the center frequency. The measured conversion gain is higher than 24 dB and the SSB noise figure is lower than 14 dB at the frequency range from 72.3 GHz to 82.5 GHz. The mismatch of the mixer RF input and the noise source output result in a ripple seen in the measurement plot. The V-band noise source (frequencies below 75 GHz) exhibits a better match than the W-band noise source (frequencies above 75 GHz). Tab. 6 shows the performance summary of the mixer.

Table 6: Mixer performance summary [23].

| SiGe bipolar technology,  | >200 GHz f <sub>T</sub> , f <sub>max</sub>       |

|---------------------------|--------------------------------------------------|

| min. eff. emitter width,  | $0.18~\mu\mathrm{m}$                             |

| ring osc. gate delay      | 3.7 ps                                           |

| Conversion gain           | >24 dB (65.0 - 90.8 GHz)                         |

|                           | >22 dB (65.0 - 94.9 GHz)                         |

| SSB noise figure          | <14 dB (72.3 - 82.5 GHz)                         |

|                           | <16 dB (66.5 - 90.0 GHz)                         |

| CP <sub>1dB</sub> (input) | -30 dBm                                          |

| Supply voltage            | -5 V                                             |

| Supply current            | 60 mA                                            |

| Chip size                 | $550 \ \mu\mathrm{m} \times 450 \ \mu\mathrm{m}$ |

### 7 Summary

Silicon-based RF ICs have been realized to demonstrate wireline, wireless and sensor applications up to 100 GHz. Finding the right match between circuit techniques and process technology is a major issue to push the circuit performance to the limits. Further advances in process technologies and circuit design will result in continuing the upward shift of the frequency limits in silicon.

### Acknowledgement

The authors would like to thank all Infineon CMOS and SiGe teams which are responsible for process technology development and fabrication.

#### References

- Urteaga, M., Scott, D., Krishnan, S., Yun, W., Dahlstrom, M., Griffith, Z., Parthasarathy, N., and Rodwell, M., Journal of Solid State Circuits, 38, pp. 1451 – 1456 (2003).

- [2] M. Mokhtari, C. Fields, and R. D. Rajavel, in GaAs IC Symposium Digest, pp. 291–294 (2002).

- [3] Li, H., Rein, H., and Suttorp, T., in 25th GaAs IC Symposium, pp. 263–266, IEEE (2003).

- [4] Rylyakov, A. and Zwick, T., in Gallium Arsenide Integrated Circuit (GaAs IC) Symposium, pp. 280– 290 (2003).

- [5] Meghelli, M., in International Solid-State Circuits Conference ISSCC, IEEE (2004).

- [6] Knapp, H., Wurzer, M., Perndl, W., Aufinger, K., Meister, T. F., and Böck, J., in Compound Semiconductor IC Symposium, IEEE (2004).

- [7] H. Knapp, M. Wurzer, T. Meister, K. Aufinger, J. Böck, S. Boguth, and H. Schäfer, in International Microwave Symposium, pp. 1067–70, IEEE (2003).

- [8] Franca-Neto, L., Bishop, R., and Bloechel, B., in International Solid-State Circuits Conference ISSCC, IEEE (2004).

- [9] Liu, R., Chang, H., Wang, C., and Wang, H., in International Solid-State Circuits Conference ISSCC, IEEE (2004).

- [10] Yamazaki, D., Yamamoto, T., Horinka, M., Nomura, H., Hashimoto, K., and Onodera, H., in International Solid-State Circuits Conference ISSCC, pp. 240–241, IEEE (2004).

- [11] Guan, X. and Hajimiri, A., in European Solid-State Circuit Conference, Florence, Italy (2002).

- [12] C. Kienmayer, R. Thüringer, M. Tiebout, W. Simbürger, and A. L. Scholtz, in IEEE Symposium on VLSI Circuits (2004).

- [13] Tiebout, M., Sandner, C., Wohlmuth, H., Da Dalt, N., and Thaller, E., in International Solid-State Circuits Conference ISSCC, IEEE (2004).

- [14] Tiebout, M., IEEE Journal of Solid-State Circuits, 39, pp. 1170-74 (2004).

- [15] Kehrer, D., H.D. Wohlmuth, M. Wurzer, and H. Knapp, Electronics Letters, 40, pp. 100–101 (2004).

- [16] Perndl, W., Wilhelm, W., Knapp, H., Wurzer, M., Aufinger, K., Meister, T. F., Böck, J., Simbürger, W., and Scholtz, A. L., in Bipolar/BiCMOS Circuits and Technology Meeting BCTM (2004).

- [17] Böck, J., Aufinger, K., Stengl, R., Boguth, S., Schreiter, R., Rest, M., Knapp, H., Wurzer, M., Perndl, W., Böttner, T., and Meister, T. F., in Bipolar/BiCMOS Circuits and Technology Meeting BCTM (2004).

- [18] Wohlgemuth, O., Paschke, P., and Baeyens, Y., in European Microwave Conference, pp. 1087–1090 (2003).

- [19] Baeyens, Y., Georgiou, G., Weiner, J. S., Leven, A., Houtsma, V., Paschke, P., Lee, Q., Kopf, R. F., Yang, Y., Chua, L., Chen, C., Liu, C. T., and Chen, Y. K., IEEE Journal of Solid-State Circuits, 37, pp. 1152– 1159 (2002).

- [20] Choudhury, D., Mokhtari, M., Sokolich, M., and Jensen, J. F., in Radio Frequency Integrated Circuits Symposium, pp. 329–332, IEEE (2004).

- [21] Masuda, S., Hirose, T., Takahashi, T., Nishi, M., Yokokawa, S., Iijima, S., Ono, K., Hara, N., and Joshin, K., in GaAs IC Symposium, pp. 99–102, IEEE (2002).

- [22] Meliani, C., Rondeau, G., Post, G., Decobert, J., Mouzannar, W., Dutisseuil, E., and Lefèvre, R., in GaAs IC Symposium, pp. 103–106, IEEE (2002).

- [23] Perndl, W., Knapp, H., Wurzer, M., Aufinger, K., Meister, T. F., Böck, J., Simbürger, W., and Scholtz, A. L., in Radio Frequency Integrated Circuits Symposium RFIC, pp. 47–50, IEEE, Texas USA (2004).

- [24] Vizmuller, P., RF Design Guide Systems, Circuits, and Equations, Artech House, Norwood, MA 02062, first edn. (1995).

- [25] Mongia, R., Bahl, I., and Bhartia, P., RF and Microwave Coupled-Line Circuits, Artech House, Norwood, MA 02062, first edn. (1999).

- [26] Meister, T. F., Schäfer, H., Aufinger, K., Stengl, R., Boguth, S., Schreiter, R., Rest, M., Knapp, H., Wurzer, M., Mitchell, A., Böttner, T., and Böck, J., in Bipolar/BiCMOS Circuits and Technology Meeting, pp. 103–106 (2003).