# TWO DIMENSIONAL MODELING OF MOS TRANSISTORS

SIEGFRIED SELBERHERR

TECHNICAL UNIVERSITY OF VIENNA

VIENNA, AUSTRIA

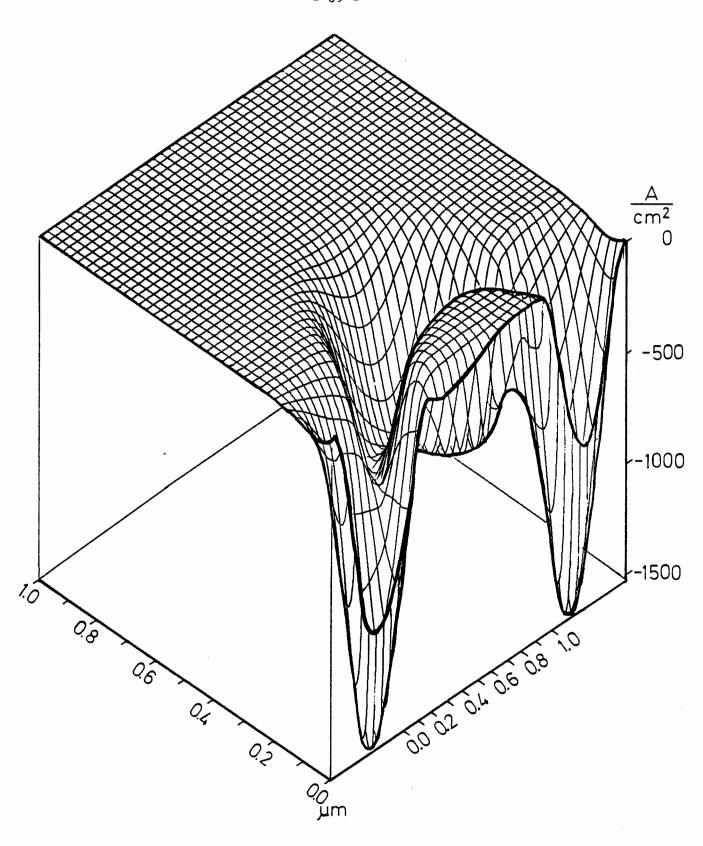

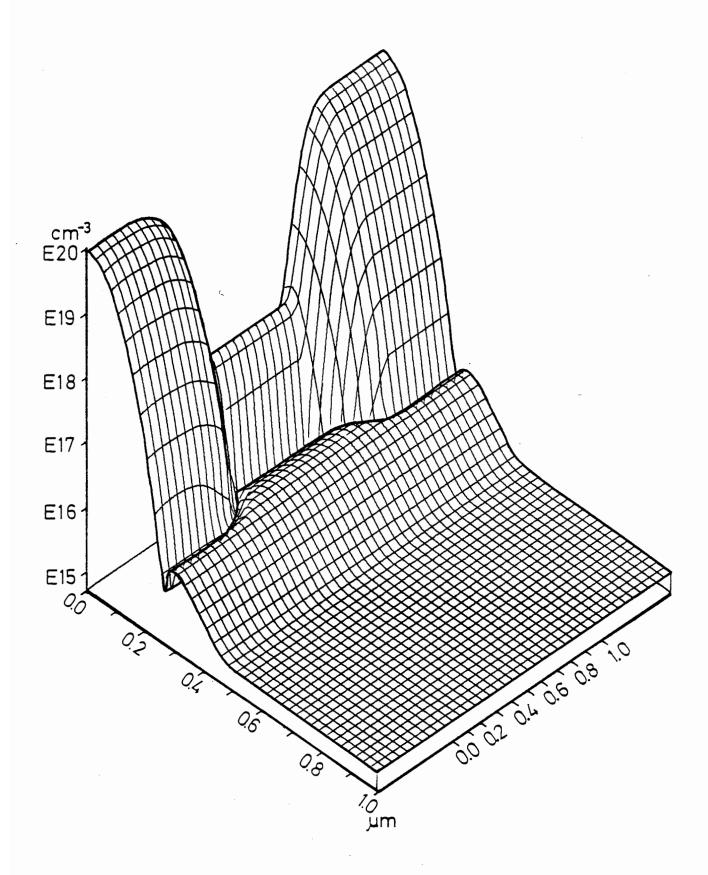

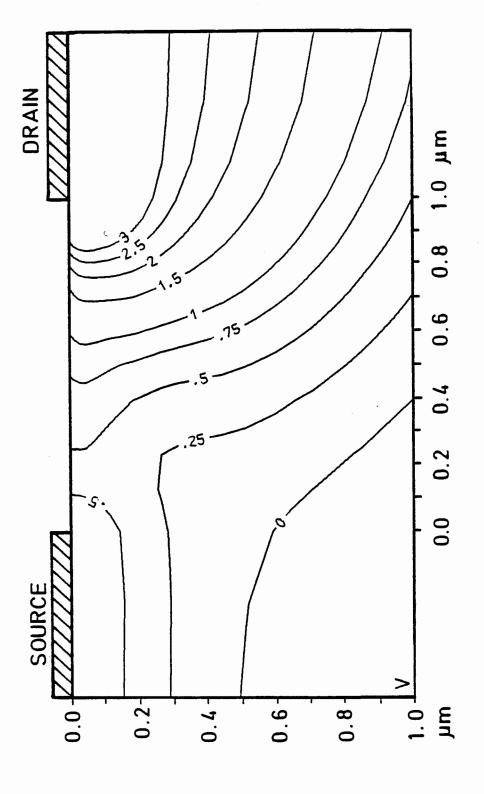

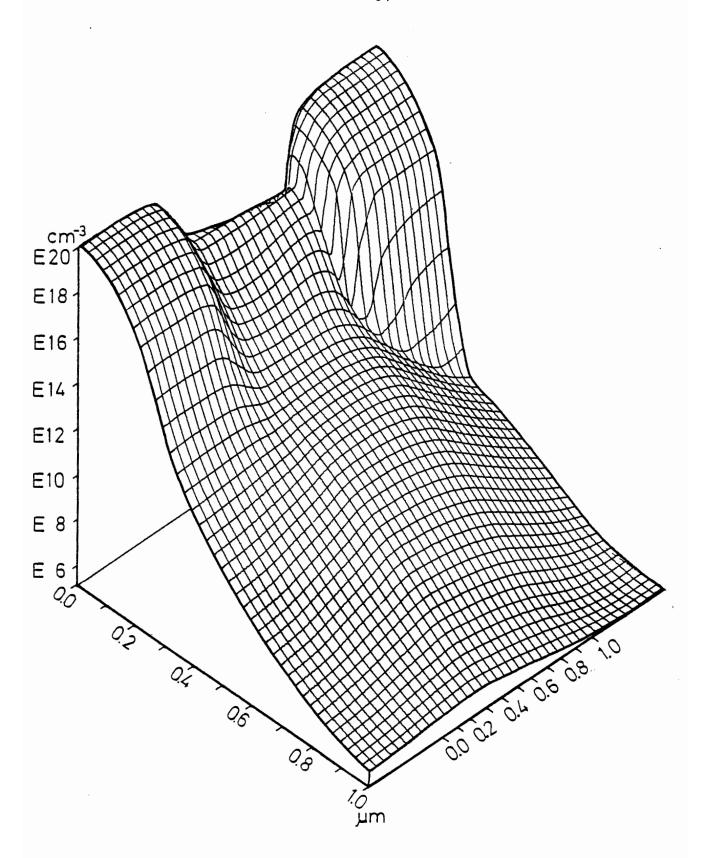

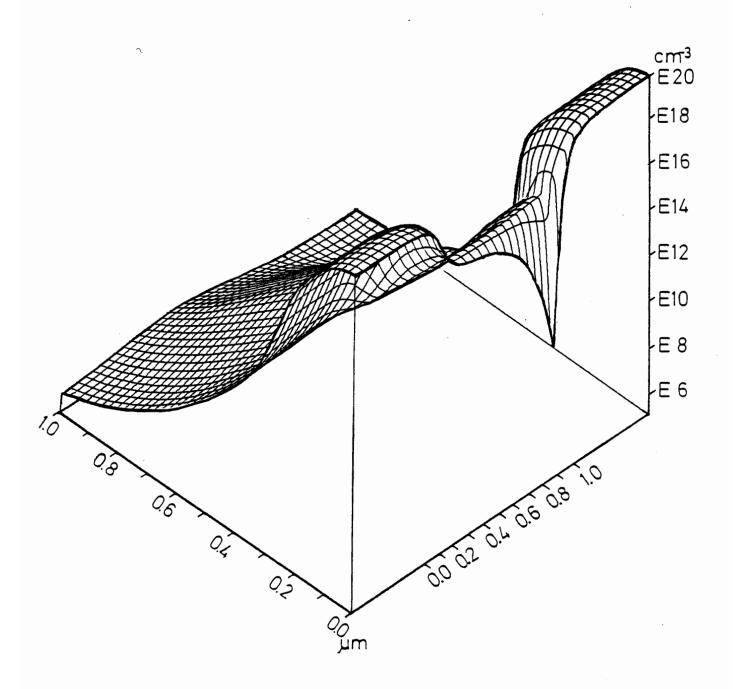

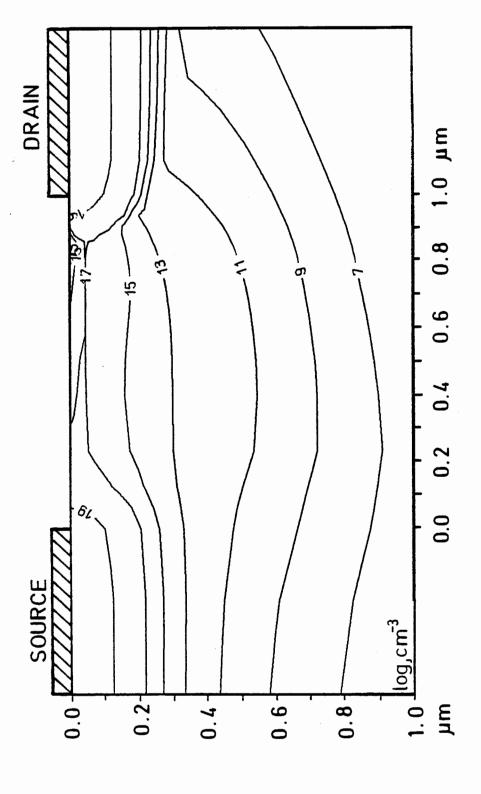

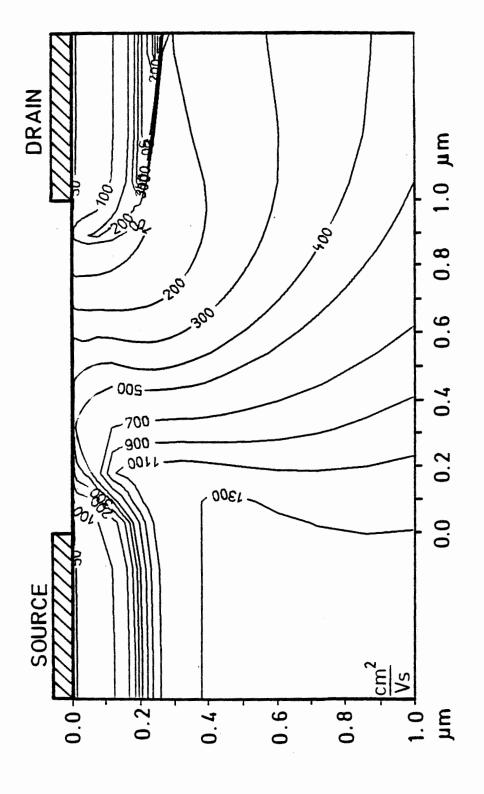

# ENGLISH TRANSLATION OF TWO DIMENSIONAL MODELING OF MOS TRANSISTORS BY SIEGFRIED SELBERHERR

SOLD TO:

COPYRIGHT (C) 1982, by SEMICONDUCTOR PHYSICS, INC.

ALL RIGHTS RESERVED.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopy, recording, or any information storage and retrieval system, without permission in writing from the publisher.

Additional copies may be ordered from:

SEMICONDUCTOR PHYSICS, INC. 639 Meadow Grove Place Escondido, CA 92027 (619) 741-3360

#### PREFACE TO THE ENGLISH TRANSLATION

This English translation of Professor Selberherr's Ph. D. thesis was undertaken because I judge that the two dimensional MOS transistor simulation program MINIMOS which is described herein will become the "SPICE" of MOS device simulation in the eighties. MINIMOS shares many of the same virtues of SPICE when it was first released by U.C. Berkeley in the early seventies. The program came at a time when the need for such a tool had become critical. No other reliable, general purpose, two dimensional MOS transistor simulator is readily available. MINIMOS is free just for the asking and is already in use in a large number of university and industrial laboratories.

Because of the ready availability and widespread use of MINIMOS there will result a worldwide community of device researchers and technology developers who will rely completely upon MINIMOS for their device simulation capability ... much in the same way as a large fraction of the integrated circuit community has relied upon SPICE for circuit simulation capability during the seventies.

MINIMOS has demonstrated itself as being a reliable and accurate simulator of small dimension MOS transistors. However, the only detailed documentation with respect to the philosophy behind and the form of the internal structure of MINIMOS is contained in Professor Selberherr's Ph.D. thesis which is written in the German language.

Since a vast number of the users of MINIMOS are native English speaking, a great void exists which this English translation is meant to fill. This translation has been completed by Semiconductor Physics, Inc., a consulting firm which specializes in device physics, modeling and characterization. The translation is meant to be a one-to-one representation of Professor Selberherr's original work.

The translation was carried out not by professional language translators, but by native English speaking device physicists whose own backgrounds coincide with the topic of the thesis ... thus the accuracy of the translation has benefitted. Furthermore, Professor Selberherr has kindly consented to proofread the entire translation and provide the necessary corrections. The equations have been largely photocopied from the original text in order to preserve accuracy.

I am indebted to Professor Selberherr for having granted permission for this translation to be commercially distributed and for having provided high quality original size figures.

May 30, 1982

Jim Smith, President

Escondido, California

SEMICONDUCTOR PHYSICS, INC.

#### Abstract of the

# DISSERTATION

"Two-dimensional Modeling of MOS Transistors"

In fulfillment of the requirements for the Degree of Doctor of Technical Science

Submitted to the Technical University of Vienna by

Dipl.-Ing. Siegfried Selberherr A-3441 Dietersdorf 61

Vienna, January 1981

#### Acknowledgment

I give special thanks to my teacher, Professor Dr. Hans Pötzl, for his great interest in the accomplishment of this work and for his helpful suggestions during countless discussions. Furthermore I thank all of my colleagues at the "Institute for Physical Electronics" for the friendly atmosphere, especially Dipl.-Ing. Alfred Schültz, without whose assistance the completion of the computer programs would have been greatly delayed.

I am deeply indebted to Siemens of Munich for the test transistors which were at my disposal.

My colleagues and friends at the "Institute for Numerical Mathematics", especially Professor Dr. Richard Weiß, Dipl.-Ing. Christian Ringhofer and associate Professor Dr. Christoph Überhuber, deserve my sincere thanks for numerous insightful conversations.

Finally I would especially like to thank the computer center of the Technical University of Vienna, Dipl.-Ing. Johannes Demel for his worthwhile suggestions with programming problems, Dipl.-Ing. Dieter Schornböck for generously providing computer time and Dipl.-Ing. Friedrich Blöser for the friendly help with the generation of graphics.

This work was supported by the "Funds for the Advancement of Scientific Research" (project no. S22/11).

### Abstract

Because very large scale integration uses MOS transistors of very small dimensions it is necessary to use computer aided modeling in order to understand their behavior. There is no analytic model in the current literature which can adequately explain the short channel effects in MOS transistors.

This work presents a two-dimensional MOS transistor model which is based only upon fundamental physical principles, and a practically oriented computer program was developed which numerically solves the model equations. The optimization of the models by appropriate assumptions is illustrated and thereby the scope of its validity is defined. Physical parameters contained in the model, as for example the carrier mobility are described with the help of a set of mathematical equations, whose realistic details are discussed. The solution of the model equations, coupled non-linear partial differential equations, is obtained by the application of numerical mathematical procedures and therewith insight with regard to their fundamental functional form is gained.

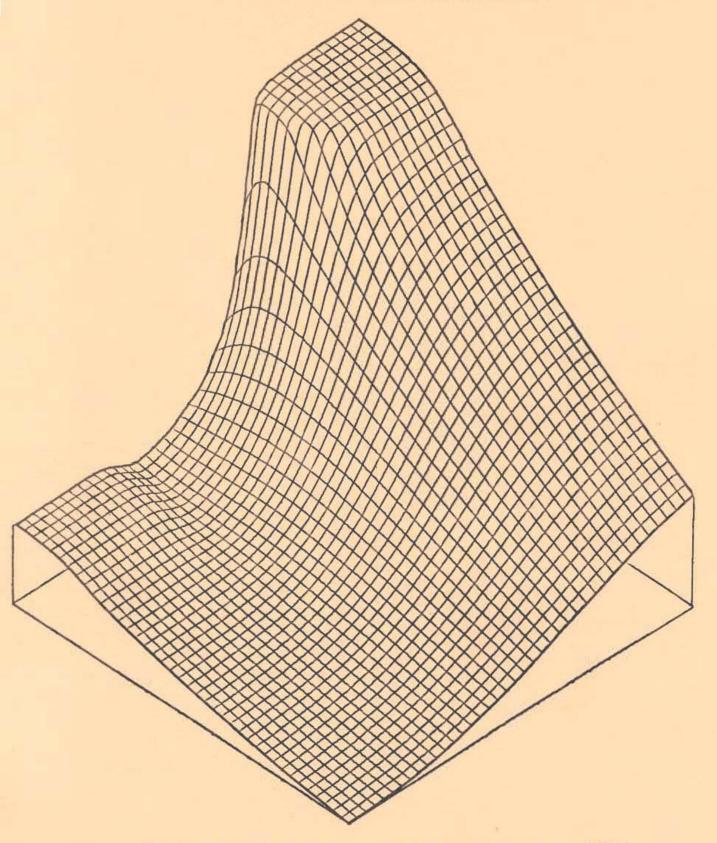

The functional efficiency of the implemented computer program is demonstrated by selected examples. It is shown, that all typical effects in miniature MOS transistors can be satisfactorily explained with the help of a two-dimensional model. An inverter circuit with submicron transistors was analyzed and examined for correct operation. Further a sensitivity analysis of a modern transistor technology is described; a strategy for the determination of the limits of the miniaturization and an estimate of reproducibility in an established process is given. It is to be expected that the developed computer program will enable faster and improved development of modern MOS transistors in regard to very large scale integrated circuits.

# TABLE OF CONTENTS

| 1. Intr | oduction                                              | 1     |

|---------|-------------------------------------------------------|-------|

|         |                                                       |       |

| 2. The  | physical model                                        | 3     |

| 2.1     | The fundamental equations                             | 4     |

| 2.1.1   | The chosen assumptions                                | 4     |

| 2.1.2   | The model equations                                   | 7     |

| 2.2     | The physical parameters                               | 9     |

| 2.2.1   | The doping profile                                    | 10    |

| 2.2.2   | The mobility                                          | 14    |

| 3. The  | numerical model                                       | 19    |

|         |                                                       |       |

| 3.1     | The linearization of the fundamental equations        | 20    |

| 3.2     | The discretization of the fundamental equations       | 23    |

| 3.2.1   | The quasiharmonic differential equation               | 26    |

| 3.2.2   | Poisson's equation                                    | 29    |

| 3.2.3   | The continuity equation                               | 32    |

| 3.2.4   | The grid generation                                   | 34    |

| 3.3     | The solution of the discretized fundamental equations | 37    |

| 4. Typi | cal applications examples                             | 40    |

| 4.1     | A didactic example                                    | 42    |

| 4.2     | The simulation of an inverter                         | 78    |

| 4.2.1   | The load transistor                                   | 80    |

| 4.2.2   | The transfer function                                 | 83    |

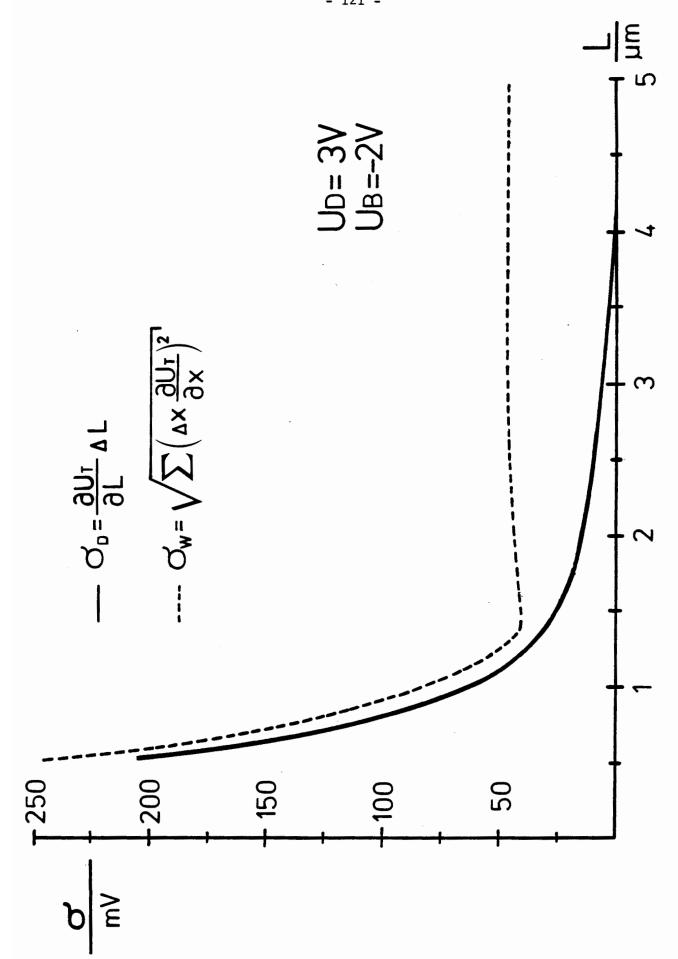

| 4.3     | Process Sensitivity                                   | 99    |

| 4.3.1   | The transistor which was analysed                     | 99    |

| 4.3.2   | The definition of the threshold voltage               | 102   |

| 4.3.3   | Sensitivities                                         | 104   |

| 4.3.4   | Global sensitivity                                    | 118   |

| 5. Conc | lusion and Outlook                                    | 123   |

| Litera  | ture cited                                            | 124   |

| Append  | ix A) The user's guide for MINIMOS*)                  |       |

| Append: | ix B) International user's of MINIMOS*)               |       |

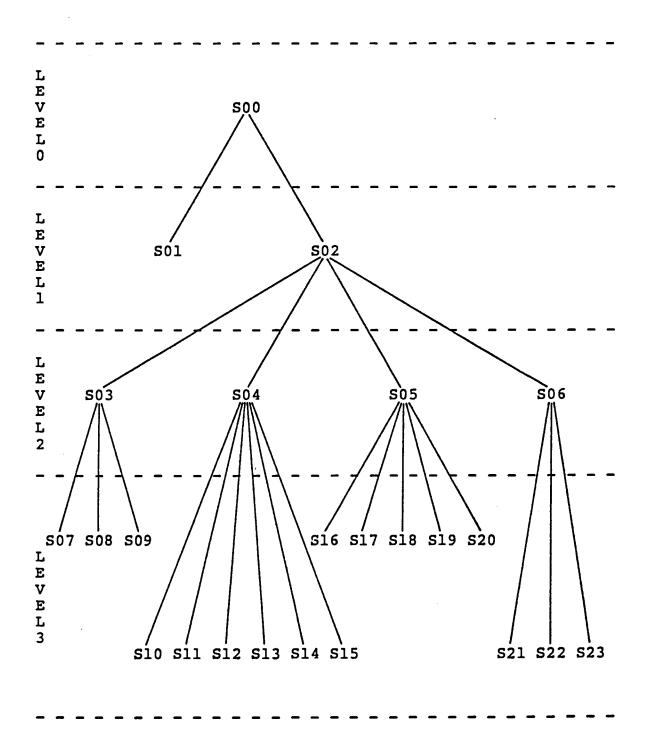

|         | ix C) The structure of MINIMOS                        | C.1   |

|         | (v D) The MINIMOS source lightingt)                   | - 3 - |

$<sup>\</sup>star$ ) not included in the present draft of the dissertation

#### Introduction

In the 20 years since 1960 when Kahng and Atalla /68/demonstrated the first functional MOS transistor, a nearly inconceivable development of these devices has occurred. Today in the decade of very large scale integrated circuits, electrical engineering without the MOS transistor is totally inconceivable. The very large scale integration (VLSI), which is mentioned here, is a technology which also absolutely requires computer aided simulation of its devices. The design of modern MOS transistors by purely experimental methods, experience and analytic models would be extremely time consuming, often very expensive and sometimes impractical from a technical viewpoint. The thus far published analytical models of MOS transistors depend upon certain assumptions, which impose certain physical restrictions, such that, in general only a limited ability to analyze and predict transistor characteristics can be achieved. Especially because of the advancing rate of miniaturization, these simple models are losing their usefulness. In order to describe the modern MOS transistor in a useful way, one is compelled to use numerical models with increased accuracy and without fundamental physical restrictions.

About 15 years ago there appeared the first, yet one dimensional, model which did not use the regional approximation as its foundation, but instead used the fundamental semiconductor transport equations /134/. The first consistent simulation using such a model was published by Gummel /58/ for the bipolar transistor. There followed a flood of analogous work with refinements and improvements in one way or another. De Mari e.g. simulated the static /35/ and dynamic /34/ operation of the P-N diode and through this work worthwhile mathematical and physical suggestions were gained.

At the end of the 1960's these one-dimensional models were extended to two coordinates. Slotboom investigated the bipolar transistor in one and two dimensions /118/, Kennedy began with the JFET /72/, Dubock performed a two dimensional analysis of the diode /41/ and transistor /40/ and Loeb attempted a two dimensional calculation for the MOS transistor. Today there exists a wide spectrum of literature on the modeling of different devices with their widely varied structures which is obvious from the bibliography which does not

claim to be complete.

The development of a two-dimensional model necessarily requires implementation in a computer program. Up until now the programs which have been developed have not been widely available. The authors had to deal with numerical stability, limited flexibility, large memory requirements and computation time requirements or low throughput.

Likewise, in this work a computer program was developed, called MINIMOS; a program aimed at consistent, numerical simulation of MINIature MOS transistors. The greatest value of the program does not lie solely in its physical foundation but also in its flexibility, modularity, dynamic memory management and portability. It should become a tool not only of academic interest but it can also be used for modeling modern transistors. The judgement, of whether or not this has been well done, naturally cannot be predicted here; an evaluation can be found in /51/ and many international institutions have indicated their interests and MINIMOS can be obtained in academic exchange for practical usage. MINIMOS should represent, with the feedback from the international users, a massive cornerstone for further modeling and design work, in that the basic understanding of the behavior of MOS transistors will be enhanced.

Chapter 2 of this work deals with the physical foundations of a two-dimensional MOS transistor model. The fundamental semiconductor equations and the permissible simplifications will be discussed and the modeling of physical parameters explained.

The theme of chapter 3 is the numerical point of view of the MOS transistor. The transformation of the fundamental equations to a form suitable for numerical solution will be discussed and the method of solution explained.

In chapter 4 it will be attempted, on the one hand, to demonstrate by examples, the functional capability of the computer program, and on the other hand, to confirm the correctness and plausibility of the underlying physical models. The selected examples should clarify the two-dimensional model, especially its breadth of applicability.

## 2. The Physical Model

In this chapter the necessary physical assumptions for a two-dimensional numerical MOS transistor model will be discussed.

Section 2.1 deals with the correct formulation of the fundamental semiconductor equations. An attempt will be made to define the scope of validity of these fundamental equations. The simplification of the general equations will be illustrated with appropriate assumptions and justified with physical arguments. The model equations which are valid for the MOS transistor (simplified fundamental semiconductor equations) will be transformed to dimensionless form and summarized.

Section 2.2 deals with the modeling of the physical parameters of the simplified fundamental equations. Special attention will be given to the simulation of the impurity distribution and the mobility. A previously unpublished model for surface scattering will be presented and the physical reasoning upon which the model is based will be explained.

#### 2.1 The Fundamental Equations

In order to accurately analyze an arbitrary semiconductor structure under all kinds of operating conditions the classical fundamental semiconductor equations must be solved. These are contained in the following five partial differential equations.

div

$$\varepsilon$$

grad  $\psi = -q \cdot (p-n+ND^+-NA^-)$  (2.1-1)

div  $\overrightarrow{J}_n - q \cdot (\partial n/\partial t) = q \cdot R$  (2.1-2)

div  $\overrightarrow{J}_p + q \cdot (\partial p/\partial t) = -q \cdot R$  (2.1-3)

$\overrightarrow{J}_n = -q \cdot (\mu_n \cdot n \cdot \text{grad } \psi - D_n \cdot \text{grad } n)$  (2.1-4)

$\overrightarrow{J}_p = -q \cdot (\mu_p \cdot p \cdot \text{grad } \psi + D_p \cdot \text{grad } p)$  (2.1-5)

Equation (2.1-1) is Poisson's equation, which characterizes the charge distribution in the semiconductor. Equation (2.1-2) describes the balance of the source and sink of electron current and eq. (2.1-3) gives the analogous relationship for hole current. These are called the continuity equations. The magnitude and direction for electron current are given by (2.1-4) and for holes by (2.1-5). This set of equations which describe the transport phenomenon in a semiconductor device was first given in closed form by Van Roosbroeck /134/ in 1950. It is to be emphasized, however, that these equations do not describe degenerate effects. In /86/, /92/, and /136/ the modifications necessary in order to take into account degeneracy (the breakdown of Boltzmann statistics and the variation of the band edge as well as the variation of the band gap) for eqs. (2.1-4) and (2.1-5) are discussed. These modifications are, however, in part not simple and lead to special problems in the boundary conditions /94/ and /135/. A consistent, but only one-dimensional, model of the degeneracy phenomenon was first published in 1979 /93/. In the relatively low doped (less than  $10^{17}~\mathrm{cm}^{-3}$ ) channels of MOS tranistors, where the current transport occurs, the degeneracy phenomenon plays absolutely no role and will not be considered here.

# 2.1.1 The Chosen Assumptions

Some assumptions in the presented model have been touched upon which significantly simplify the solution of the equations without a considerable

loss of accuracy. The assumptions should in no way alone remove the difficulties as one might falsely conclude from the last sentence. On the contrary, in the first place, the throughput and computational speed for the solution of the fundamental equations by an obviously necessary computer program should be raised if the program is to become a worthwhile tool. The program developed in the scope of this work shall perform in developmental efforts, sometimes with very many variables, not only for the infrequent simulation of academic interest, but also for the experienced transistor designer.

\* Only a static solution is sought. This assumption is of fundamental importance, thereby the order of the partial differential equations is reduced. When considered from a mathematical point of view, this leads to a significant change in the formulation of and insight into the problem. By way of the suppression of the time dependent term a parabolic problem is converted to an elliptic problem, whereby another point of view must be adopted. Contributions toward the transient solution of the semiconductor equations have indeed already been published e.g. /10/, /30/, /84/, /100/, and /102/, however the authors themselves acknowledge that these solutions are only of academic interest and the programs developed by these authors have exhibited limited flexibility and therefore are of little practical value. However, relatively new theoretical work /76/, /91/ has given hope that in the near future a useful model for a two dimensional transient analysis will be developed.

| an/at = 0 | (2.1-6) |

|-----------|---------|

| ap/at = 0 | (2.1-7) |

\* On the grounds of the lattice structure of silicon and the amorphous nature of oxide, their dielectric constants are isotropic. The dielectric constants in equation (2.1-1) can be taken outside the divergence operator.

$$\epsilon_{si} = const$$

(2.1-8)

$\epsilon_{\text{ox}} = \text{const}$  (2.1-9)

\* Total ionization of the impurities will be assumed, which is justified for the temperature range of 250K to 450K to which this model is limited /121/.

$$C = N_D - N_A = N_D^+ - N_A^-$$

(2.1-10)

\* Degeneracy phenomena, as has already been mentioned, will not be considered. The intrinsic carrier concentration will be taken as constant.

$$n_i = const$$

(2.1-11)

\* Majority carrier current is neglected. This assumption represents the most significant limitation. The a priori assumption of negligible majority carrier current prevents a direct and consistent calculation of substrate current and an analysis of the breakdown behavior. However, though an integration of the ionization rate throughout the entire transistor, a satisfactory evaluation of the substrate current can be made /131/, and the onset of avalanche breakdown under high field conditions can be found. In principle this assumption is justified, inasmuch as two of the five fundamental equations become trivial and do not need to be solved.

$$\vec{J}_p = 0$$

(for n-channel transistors) (2.1-12)

$$\vec{J}_p = 0$$

(for p-channel transistors) (2.1-13)

\* The temperature throughout the entire transistor is constant and can be varied over the interval of 250K to 450K.

$$T = const (2.1-14)$$

\* The carrier distribution is described by Boltzmann statistics. This assumption states that heavy doping and degeneracy effects need not be considered and therefore are not a problem.

$$n = n_i \cdot e^{(\psi - \phi_n)/U_T}$$

(2.1-15)

$$p = n_i \cdot e^{(\phi p - \psi)/U_T}$$

(2.1-16)

\* The validity of the Einstein-Nernst relation is assumed. The importance of this assumption is tied to Boltzmann statistics and the original form of the fundamental semiconductor equations, in that these formulations do not distinguish between the electron temperature and the lattice temperature.

$$D_{n} = \mu_{n} \cdot U_{T}$$

(2.1-17)

$D_{p} = \mu_{p} \cdot U_{T}$  (2.1-18)

\* All contacts are considered to be ohmic. The space charge vanishes at the contact, and the carrier distribution is in thermal equilibrium.

# 2.1.2 The Model Equations

In consideration of the chosen assumptions found in the last section the fundamental equations are simplified considerably. But before the simplified equations are summarized, a normalization into dimensionless form will be carried out following De Mari /35/. The normalization constants for electric charge, the dielectric constant, the diffusion constant, the flux and the potential will be determined a priori, whereupon everything else in the equations is constrained to follow. The important normalization factors are listed in figure 2.1-1.

| Dimension           | <u>Units</u>        | Normalization factor                                                                                                                                                                     |

|---------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electric charge     | As                  | q                                                                                                                                                                                        |

| Diffusion constant  | cm <sup>2</sup> /s  | $D_0 = 1 \text{ cm}^2/\text{s}$                                                                                                                                                          |

| Dielectric constant | As/Vcm              | ε <sub>si</sub>                                                                                                                                                                          |

| Flux                | cm <sup>-3</sup>    | n <sub>i</sub>                                                                                                                                                                           |

| Potential           | v                   | U <sub>T</sub>                                                                                                                                                                           |

| Length              | cm                  | $\mathbf{x}_{0} = \left( \left( \mathbf{\varepsilon}_{si} * \mathbf{U}_{T} \right) / \left( \mathbf{q} * \mathbf{n}_{i} \right) \right)^{\frac{1}{2}}$ $\mathbf{x}_{0} / \mathbf{D}_{0}$ |

| Time                | s                   | $\mathbf{x_0}^2/\mathbf{D_0}$                                                                                                                                                            |

| Mobility            | cm <sup>2</sup> /Vs | D <sub>O</sub> /U <sub>T</sub>                                                                                                                                                           |

| Current density     | A/cm <sup>2</sup>   | $J_0 = q*D_0*n_i/x_0$                                                                                                                                                                    |

Figure 2.1-1: The normalization factors

The postulates (2.1-12) and (2.1-13) necessarily require a distinction between the equations for n-channel and p-channel transistors. Consequently for n-channel transistors the following equations hold:

div grad

$$\psi = e^{\psi - \phi_n} - e^{\phi p^{-\psi}} - C$$

(2.1-19)

div  $\vec{J}_n = R$

$\vec{J}_n = -\nu_n \cdot n \cdot \text{grad } \phi_n$

$\phi_p = \text{const}$  (which implies:  $\vec{J}_p = 0$ )

and for the p-channel transistor the following equations hold:

div grad

$$\psi = e^{\psi - \phi} n - e^{\phi} p^{-\psi} - C$$

(2.1-20)

div  $\vec{J}_p = -R$

$\vec{J}_p = -\mu_p \cdot p \cdot grad \phi_p$

$\phi_n = const$  (which implies:  $\vec{J}_n = 0$ )

Equations (2.1-19) and (2.1-20) actually describe a coupled system of two nonlinear partial differential equations, which can only be solved numerically. It should probably also be mentioned here, that all quantities in both of these systems of equations appear dimensionless, which implies normalized variables. For the purpose of clarity these were not characterized by explicit indices.

# 2.2 The Physical Parameters

The model equations derived in the last section (2.1-19) and (2.1-20) contain several physical parameters whose modeling will be discussed next. The importance of these parameters may not be underrated, in that their accuracy directly determines the quantitative validity of the total simulation results.

\* The thermal voltage  $U_{\rm T}$  is the simplest parameter. It is only required for normalization (see section 2.1.2) and is only dependent upon the simulation temperature.

$$U_{T} = k \cdot T/q \quad (V) \tag{2.2-1}$$

\* The intrinsic carrier concentration is modeled as being only temperature dependent. The formula used is very simple and does not account for the temperature dependence of the band gap and only roughly accounts for the temperature dependence of the band edge /50/. These temperature dependencies however are not necessary because the intrinsic carrier concentration is only required for normalization and furthermore the temperature is a global quantity. The narrowing of the band gap due to heavy doping /89/, /119/ can also be neglected.

$$n_i = 3.88 \cdot 10^{16} \cdot r^{1.5} \cdot e^{-7000/T} \text{ (cm}^{-3}\text{)}$$

(2.2-2)

\* The thermal generation will be simulated by means of simple Shockley-Read-Hall levels. The neglect of the majority carrier current in general appears to give these levels no meaning. For the intrinsic current transport in the channels of MOS transistors it is also true that on the grounds that the majority carrier current is absent, no recombination is possible. Without thermal generation, which would be naturally described by these levels, an absolutely unrealistic carrier depletion arises in the reverse biased drain/substrate diode. These levels will be chosen for stabilization in order to eliminate a numerical problem which may arise due to an unrealistically low density. The recombination centers are assumed to be in the middle of the forbidden band. The lifetimes will not be modeled /31/, but will instead be

assumed to be constant.

$$R = \frac{p \cdot n - n_i^2}{\tau_p \cdot (n + n_i) + \tau_n \cdot (p + n_i)} \quad (cm^{-3}s^{-1})$$

(2.2-3)

The remaining parameters, the doping profile and the mobility, are of primary importance in the behavior of modern MOS transistors and must be modeled with greater effort.

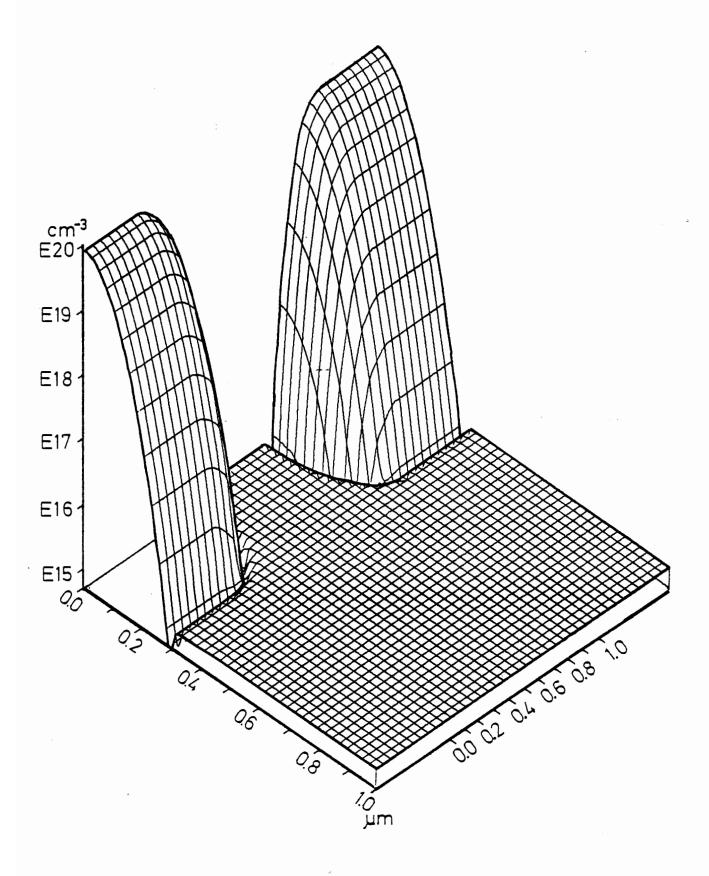

#### 2.2.1 The Doping Profile

The most important input parameter for the simulation of miniature transistors is the doping profile. International research in the area of twodimensional doping profiles is just now beginning. Because of the difficulties hidden in the modeling refinements of the diffusion of the impurities; the modeling of the diffusion constant; the effects due to interaction of different dopants, the oxide growth and similar questions, an interfaculty cooperation is needed in order to achieve concrete progress in these areas. Interesting results and aspects can be inferred from /106/ about two-dimensional implantation effects and from /107/, /130/, and /141/ about two dimensional diffusion effects. The possibility of obtaining closed form analytic solutions by realistic model refinements is as small for the diffusion problem as it is for the electrical transport problem. importance of coupling between two-dimensional process simulation and twodimensional transistor modeling will surely arise in the highest degree in the near future because of progressive miniaturization /20/, and will provide great stimulus for scientific contributions in many places.

In MINIMOS there are two principle possibilities available for use in specifying the doping profile. SUPREM, the Stanford University Process Engineering Model Program /6/ can be used to calculate, with very good accuracy, a one-dimensional channel profile and source/drain profile, whereby in the lateral direction an adjustment with equation (2.2-4) will be made.

$$C(x,y) = C((y^2 + max(x/f,0)^2)^{1/2})$$

(2.2-4)

In the above equation y = 0 represents the interface; x = 0 denotes the edge of the gate mask at the source; the oxide mask lies in the negative x

direction. Equation (2.2-4) permits control of the underdiffusion with the help of the parameter 'f', which in practical cases lies between 0.5 and 0.9. This equation does not take into account the outdiffusion in the positive x direction.

The second facility for the specification of the doping profiles uses an analytic approach, which in many cases provides sufficient accuracy. This approach is based principally upon the work of Lee /78/, /79/.

A predeposition can be simulated with equation (2.2-5). The parameters required here are the surface concentration  $N_{\rm S}$ , the diffusion time t, and also the diffusion constant D for the doping element and the diffusion temperature. A predeposition can only be simulated for the source/drain regions, because it is only meaningful in those regions. Similar approaches for modeling the predeposition are given in /19/ and /70/.

$$1d = 2 \cdot \sqrt{D \cdot t}$$

(2.2-5)

$C_p(x,y) = 0.5 \cdot N_g \cdot e^{-(y/1d)^2} \cdot erfc(x/1d)$

Ion implantation and diffusion can be simulated with the set of equations (2.2-6). The parameters which must be specified are the dopant element (which affects  $R_p$ ,  $\Delta R_p$  and D), the implantation dose "DOSE", the implantation energy (which defines  $R_p$  and  $\Delta R_p$ ), the oxide thickness  $T_{\text{iox}}$  (which influences  $R_p$ ), the diffusion time t, and the diffusion temperature (hidden in the diffusion constant). When double channel implantations are performed, the individual profiles are superimposed.

It is further taken that the source/drain profile and the channel profile are simply superimposed, that is, interaction of the diffusions is neglected.

The diffusion constants are taken as constant in (2.2-5) and (2.2-6). This is justifiable for the diffusion of the channel profile (relatively low surface doping), but not for the source/drain diffusions. Because, at the present, no closed form analytic representation for diffusion with a nonconstant diffusion coefficient is known. No other alternative is available. One can, however, with some degree of skill with an arbitrary time or diffusion temperature, cause the pn transition region to appear as if the diffusion were done with dopant dependent and field dependent diffusion coefficients. The diffusion coefficients will be calculated by way of the traditional exponential equation and the data from figure 2.2-1.

| $D = D_0 - e^{T_a/T}$ |         |                                                    |                        | (2.2-7) |

|-----------------------|---------|----------------------------------------------------|------------------------|---------|

|                       | Element | D <sub>0</sub> /(cm <sup>2</sup> s <sup>-1</sup> ) | T <sub>a</sub> /(K)    |         |

|                       | В       | 0.5554                                             | -3.975·10 <sup>4</sup> |         |

|                       | P       | 3.85                                               | -4.247·10 <sup>4</sup> |         |

|                       | SB      | 12.9                                               | -4.619·10 <sup>4</sup> |         |

|                       | λ       | 24.                                                | -4.735·10 <sup>4</sup> |         |

Figure 2.2-1: The diffusion constants.

Furthermore, the parameters  $R_p$  and  $\Delta R_p$ , the projected range and the associated standard deviation, which appear in equations (2.2-5) and (2.2-6) must also be modeled. These parameters are tabulated in /55/ as functions of the implantation energy according to the LSS theory. That table, even though relatively coarse, can only be implemented in a computer program in an unwieldly fashion, and is interpolated by a best-approximation polynomial for the projected range and the standard deviation, thereby minimum memory storage requirements and very fast output can be achieved /115/.  $R_p$  and  $\Delta R_p$ , take on the following forms.

$$Rp = \prod_{i=1}^{n} x^{i}$$

$$\Delta Rp = \prod_{i=1}^{n} x^{i}$$

(2.2-8)

In (2.2-8) x is understood to be the implantation energy. The rank n of these polynomials lies in each case, according to the implantation element, between 2 and 5. The polynomial coefficients for  $(R_{psi})$  and  $(\Delta R_{psi})$  the projected range and standard deviation in silicon are given in figures 2.2-2 and 2.2-3 respectively and in figure 2.2-4 for  $(R_{pox})$  the projected range in silicon dioxide.

| Element               | · <b>B</b>              | P                       | SB                       | λ                        |

|-----------------------|-------------------------|-------------------------|--------------------------|--------------------------|

| <b>a</b> <sub>1</sub> | 3.338.10-3              | 1.259.10-3              | 8.887.10-4               | 9.818.10-4               |

| a <sub>2</sub>        | -3.308·10 <sup>-6</sup> | -2.743·10 <sup>-7</sup> | -1.013.10-5              | -1.022·10 <sup>-5</sup>  |

| a <sub>3</sub>        |                         | 1.290.10-9              | 8.372·10 <sup>-8</sup>   | 9.067·10 <sup>-8</sup>   |

| a4                    |                         |                         | -3.056·10 <sup>-10</sup> | -3.442·10 <sup>-10</sup> |

| a <sub>5</sub>        |                         |                         | 4.028.10-13              | 4.608.10-13              |

Figure 2.2-2: Coefficients for  $\mathbf{R}_{\mathbf{p}}$  in silicon.

The dimension of the coefficients  $a_{\bf i}$  ,  $b_{\bf i}$  in figures 2.2-2 through 2.2-4 is (  $\mu m/keV^{\bf i}$  ).

| Element        | В                        | P                       | SB                       | λ                        |

|----------------|--------------------------|-------------------------|--------------------------|--------------------------|

| b <sub>1</sub> | 1.781.10-3               | 6.542-10-4              | 2.674.10-4               | 3.652-10-4               |

| ь <sub>2</sub> | -2.086·10 <sup>-5</sup>  | -3.161·10 <sup>-6</sup> | -2.885·10 <sup>-6</sup>  | -3.820·10 <sup>-6</sup>  |

| b <sub>3</sub> | 1.403.10-7               | 1.371.10-8              | 2.311·10 <sup>-8</sup>   | 3.235·10 <sup>-8</sup>   |

| b <sub>4</sub> | -4.545·10 <sup>-10</sup> | -2.252.10-11            | -8.310·11 <sup>-10</sup> | -1.202-10 <sup>-10</sup> |

| b <sub>5</sub> | 5.525.10-13              |                         | 1.084.10-13              | 1.601-10-13              |

Figure 2.2-3: Coefficients for  $\Delta R_p$  in silicon.

| Element        | В                       | P                       | SB                       | λ                        |

|----------------|-------------------------|-------------------------|--------------------------|--------------------------|

| a              | 3.258.10-3              | 9.842-10-4              | 7.200.10-4               | 7.806-10-4               |

| a 2            | -2.113·10 <sup>-6</sup> | -2.240·10 <sup>-7</sup> | -8.054·10 <sup>-6</sup>  | -7.899·10 <sup>-6</sup>  |

| <b>a</b> 3     |                         |                         | 6.641.10-8               | 7.029·10 <sup>-8</sup>   |

| a <sub>4</sub> |                         |                         | -2.422·10 <sup>-10</sup> | -2.653·10 <sup>-10</sup> |

| a <sub>5</sub> |                         |                         | 3.191·10 <sup>-13</sup>  | 3.573·10 <sup>-13</sup>  |

Figure 2.2-4: Coefficients for  $R_{\rm D}$  in silicon dioxide.

When implanting through a protective oxide, the actual range must be reduced with equation (2.2-10), in which the projected ranges for silicon  $(R_{psi})$  and for oxide  $(R_{pox})$  and the oxide thickness  $(T_{iox})$  are the required parameters /108/.

$$Rp = Rp_{si} \cdot (1 - T_{iox}/Rp_{ox})$$

(2.2-10)

# 2.2.2 The Mobility

The mobility is the most complex parameter in the fundamental semiconductor equations. Its modeling is of eminent importance, since any error in the mobility immediately influences the current density distribution in the transistor. A comparison of simulation results and measurements is as yet only possible by way of current characteristics, whereby the simulation is calculated pointwise through the integration of the current density, so that errors in the current density naturally cause a direct error in the current.

For a correct modeling of the mobility, the different underlying physical mechanisms must be taken into consideration. The basic mobility in high purity, field free silicon is determined by lattice scattering. In the following, this basic mobility will always be designated with  $\mu_L$  (lattice). It is only temperature dependent and it can be modeled in a relatively simple way by way of a power law /64/, /80/. Equation (2.2-11) gives the applicable model of the basic mobility, whereby the indices n and p in the coefficients signify the identification of electrons and holes respectively.

$$\mu_{L}(T) = A \cdot T^{-\gamma}$$

(cm<sup>2</sup>/Vs) (2.2-11)

$A_{n} = 7.12 \cdot 10^{8}$   $A_{p} = 1.35 \cdot 10^{8}$

$\gamma_{n} = 2.3$   $\gamma_{p} = 2.2$

Only the basic mobility has been described so far, with mention already made of the scattering in high purity, field free silicon. Through the existence of impurities this basic mobility will be decreased by way of two dimensional scattering of the free charge carriers due to impurities. This process is temperature dependent as is lattice scattering. A whole range of formulations have been published in order to model these effects. Many are based upon theoretical considerations /36/, /80/; quite a lot however are heuristic in nature but they are very good when their quantitative accuracy is checked experimentally /5/, /18/, /110/. The heuristic formulations have in general a substantially more simple structure with equal accuracy, so that in this work they will be given preference. Equation (2.2-12) will be used for concrete modeling of the temperature dependence of the composite lattice and impurity scattering mobility  $\mu_{\rm LT}$  in doped, but field free silicon.

$$\mu_{LI}(N,T) = \mu_{L}(T) \cdot a + \mu_{min} \cdot (1-a) \quad (cm^{2}/Vs) \qquad (2.2-12)$$

$$a = \frac{1}{1 + (T/300)^{6} \cdot (N/N_{0})^{\alpha}}$$

$$N = N_{D}^{+} + N_{A}^{-}$$

$$\mu_{minn} = 55.24 \qquad \mu_{minp} = 49.7$$

$$\delta_{n} = -3.8 \qquad \delta_{p} = -3.7$$

$$\alpha_{n} = 0.73 \qquad \alpha_{p} = 0.7$$

$$N_{0n} = 1.072 \cdot 10^{17} \qquad N_{0p} = 1.606 \cdot 10^{17}$$

Because in the MOS transistor the current flows mainly at the surface of the silicon, in the boundary layer which lies inside the inversion channel, a further scattering mechanism, the surface scattering, absolutely must be taken into account. It is established, however with great regret, that a model with a physical foundation is impossible, because theoretically this scattering process is not sufficiently understood. From this point on a further description of the surface scattering can only use heuristic arguments, which are based upon former intuitive reasoning. Regretably it is almost impossible to make a measurement of the surface mobility, which could directly verify a heuristic formula, because effectively one only measures the average mobility in the channel, however, a two dimensional mobility distribution is required for a two dimensional simulation. It is also safe to say, that the measurement of the effective mobility in the inversion channel exhibits great difficulty, which can only be mastered with satisfactory accuracy in outstanding laboratories /109/.

There is very little written about the heuristic considerations for models of the surface mobility /142/; the previously established considerations are simple and unsatisfactory. Experimental results are published in /124/, and future progress seems hopeful with respect to the modeling of the surface mobility.

From the above mentioned arguments a likewise heuristic formulation for a model of surface mobility and its correction with lattice and impurity mobility has been developed, with which plausible simulation results and a satisfactory accuracy can be obtained. With the help of the complete formula in (2.2-13) it is possible to include the gate controlled electric field dependence of the surface roughness scattering in the model. All effects describing the mobility which have been discussed up to this point are represented by the symbol  $\mu_{\rm LTS}$  (lattice, impurity, surface).

$$\mu_{LIS}(y, E_{p}, E_{t}, N, T) = \mu_{LI}(N, T) \cdot \frac{y+y_{T}}{y+b\cdot y_{T}} (cm^{2}/v_{S}) \quad (2.2-13)$$

$$y_{T} = y_{0}/(1+E_{p}/E_{p0})$$

$$b = 2+E_{t}/E_{t0}$$

$$E_{p} = \max(0, (E_{x}\cdot J_{x}+E_{y}\cdot J_{y})/(J_{x}^{2}+J_{y}^{2})^{1/2})$$

$$E_{t} = \max(0, (E_{x}\cdot J_{y}-E_{y}\cdot J_{x})\cdot J_{x}/(J_{x}^{2}+J_{y}^{2}))$$

$$y_{0n} = 5\cdot 10^{-7} \qquad y_{0p} = 4\cdot 10^{-7}$$

$$E_{p0n} = 10^{4} \qquad E_{p0p} = 8\cdot 10^{3}$$

$$E_{t0n} = 1.8\cdot 10^{5} \qquad E_{t0p} = 3.8\cdot 10^{5}$$

The lattice/impurity mobility at the surface (y = 0) is reduced by the factor 1/b; and at a distance  $y_r$  it is reduced by the factor 2/(1+b); and at greater distances from the surface it naturally follows that there is no reduction in the mobility. yr represents a characteristic length, which describes the range of influence of the surface. This range is a function of  $E_{

m p}$ , the field strength component, which lies parallel to the current direction. The formulation for y produces a reduction in the range of the surface scattering by greater field strength parallel to the current direction, thereby velocity saturation appears, which will be discussed in the The remaining physical consideration is, that the charge carrier, which is moving at saturated velocity, experiences less influence due to the surface. The parameter b in (2.2-13) descibes the extent of influence of the surface scattering. It is a function of Et, the projection of the field strength component normal to the current direction in the direction normal to the surface. The formulation for b rests upon the consideration, that the charge carriers are pressed against the surface by an electric field, which results in a greater scattering, such that a greater mobility reduction results.

The last relevant physical effect for modeling the mobility is the velocity saturation. For this effect there are no useful physical fundamental arguments of high accuracy, so that analogously to the treatment for the surface scattering a simple heuristic model must be derived. Formulations for

such models exist in the relevant literature in sufficient quantity /17/, /18/, /64/, /65/, /110/. The formulation used in this work is quoted from established literature in the form of a plausible common denominator. With the addition of the velocity saturation one obtains the formula (2.2-14), in which  $E_p$ , as in (2.2-13), is the field strength component in the current direction, and  $v_s$  is the saturation velocity. Formula (2.2-14) is considered to be a structure of a type of Mathiessen's rule /111/ with a correlation weight (- $\beta$ ).

$$\mu_{\text{tot}}(y, E_{p}, E_{t}, N, T) = (\mu_{\text{LIS}}(...)^{\beta} + (v_{s}/E_{p})^{\beta})^{1/\beta} \qquad (2.2-14)$$

$$E_{p} = \max(0, (E_{x} \cdot J_{x} + E_{y} \cdot J_{y}) / (J_{x}^{2} + J_{y}^{2})^{1/2})$$

$$v_{sn} = 1.53 \cdot 10^{9} \cdot T^{-0.87} \qquad v_{sp} = 1.62 \cdot 10^{8} \cdot T^{-0.52}$$

$$\beta_{n} = -2 \qquad \beta_{p} = -1$$

# 3. The Numerical Model

A central theme of the work presented here is the transformation of the physical model of the MOS transistor, which was established in the last chapter, into a numerical model. This numerical model was realized in the form of a computer program, which permitted the verification of the numerical model, as well as the physical model in wider scope. MINIMOS — so the program was named contains all of the necessary software for the solution of the semiconductor equations and the modeling of the physical parameters. In this chapter the numerical assumptions and background, that are necessary for the establishment of a program such as MINIMOS will be treated and discussed.

In section 3.1 the alternatives for the linearization of the fundamental equations will be given and the procedures implemented in MINIMOS will be explained.

Section 3.2 deals with the discretization of the fundamental equations. The discretization of a problem, which is presented as a transformation from an analytic formulation to a numerical formulation, will first be presented as carried out in general for the quasi-harmonic differential equation, a generalized type for the linearization of Poisson's equation and the continuity equation and it will then be specialized for these equations.

The solution of the discretized fundamental equations will be discussed in section 3.3 An overview of the available existing methods will be presented and their consequences singled out for the reader.

### 3.1 The Linearization of the Fundamental Equations

In the last chapter a system of nonlinear partial differential equations was presented, which describe the current transport in an MOS transistor, and which must be linearized before it can be solved numerically. The system of equations examined in the following are exclusively for N-channel transistors. The equations for the P-channel transistor are structurally identical and thereby all established considerations will be valid. For purposes of clarity this system is presented again here in normalized form:

The classical mathematical way to the solution of this kind of system is the use of a Newton procedure with eventual damping and/or extrapolation /99/, /104/ for the simultaneous solution of the complete system. A shortcoming of this method however is the considerable storage requirement which is required for the Jacobian matrix of the system. A more important advantage to be noted is that this procedure exhibits quadratic limiting convergence.

An alternative means for solving this system of equations is the application of a block nonlinear iteration procedure, by which a Newton-like formulation is not applied to the complete system. Instead a Newton-like formulation is established for each of the differential equations keeping constant the secondary independent variables for which an individual choice

must be found for each specific problem. From well known authors /15/, /30/ comparisons of both of these procedures have been made, and the conclusions conceded, that the block-nonlinear iteration procedure is preferred for a wide spectrum of applications. The procedures were first published in explicit form for application to semiconductor equations by Gummel /58/, who therein gave an intuitive and physically based derivation. In the relevant literature it is often designated as the Gummel algorithm.

A mathematical convergence proof for the application of the blocknonlinear iteration procedure to the semiconductor equations is not known and in considering the complexity of the problem, such a proof may not be trivial.

As a complement to the somewhat heuristic theory of the Gummel algorithm, the works /11/ and /127/ are mentioned, which however present only insignificant improvements.

The practical procedure followed is: One solves Poisson's equation with fixed  $\phi_n$  and thereafter the continuity equation with constant  $\psi$ . This process is iteratively repeated until one has obtained a consistent solution for  $\psi$  and  $\phi_n$ . The necessary accuracy is an important point to be stated for the solution of the individual equations. The accuracy is verified by beginning the iteration process with small accuracy requirements and successively increasing them during the iteration under consideration of the global errors from the right hand sides of (3.1-1) and (3.1-2).

One first applies the Newton-like formulation for the linearization of Poisson's equation (3.3-1) and, therefore one obtains, after simple algebraic transformation:

$$\psi^{k+1} = \psi^k + \delta$$

.

div grad  $\delta - \delta \cdot (n+p) = n - p - C - \text{div grad } \psi^k + O(\delta^2)$

mit:  $n = e^{\psi^k - \phi^k}n$

$p = e^{\psi p - \psi^k}$  (3.1-3)

Because of the exponential nonlinearity of Poisson's equation it is mathematically significant to propose a damping of the potential increment in order to prevent an eventual overshooting of the Newton procedure. This can e.g. be done in the following manner:

$$\psi^{k+1} = \psi^k + \delta/(1+|\delta|/1im)$$

(3.1-4)

This form of damping, the so called hyperbolic damping, is continuous with 'lim' signum ( $\delta$ ) as the boundary value for  $\delta$  as opposed to  $\infty$  and it has been well proven by all test calculations. 'lim' is in the case of Poisson's equation, when it is represented in its normalized form as in this work, assigned the order of magnitude of 0.25. This way of damping is arbitrary; it has however resulted in a monotonic convergence in all calculations for the Newton procedure for Poisson's equation. The relevant literature offers a wide spectrum of similar variants /14/, /99/.

The linearization of the continuity equation (3.1-2) can be achieved by the application of a Newton-like formulation in a completely analogous way as was briefly explained for Poisson's equation. By suitable substitution of the independent transformation the continuity equation is only very weakly nonlinear, such that, as will become clear in subsection 3.2.3, a linearization can in general be avoided.

#### 3.2 The Discretization of the Fundamental Equations

The differential equations which, in the last section, resulted from the linearization of the complete system of semiconductor equations possess no closed analytic solution and their solution must be found numerically. The first step toward a numerical solution is the partitioning of the regions, in which the differential equations are to be solved under consideration of their boundary conditions, into a finite number of subregions, in which the desired solution to the problem can be approximated with the desired accuracy through simple functions; the equations must be discretized. One must be very careful, because in no case with this procedure does one obtain an exact solution to the analytically formulated problem, instead in the best case an exact solution to the transformed, discrete problem, which, depending upon the fineness of the partioning of the total region and the type of approximate functions in the subregions, represents a more or less good approximate solution to the analytically formulated problem.

There are many classical methods, which propose constructive possibilities for the subdivision of the total region and the choice of approximate functions. In this work a variation of the method of finite differences was used, the five point discretization, which was preferred by most other authors in their work on two dimensional modeling. Examples are the dissertations of Heimeier /62/, of Jesshope /66/ and of Mank /84/ and the review article by Kani /69/ which covered modeling activities in Japan. Discretizations of higher orders were not taken into consideration because of their complexity with respect to programming and possibly for the same reason they also do not appear in the literature.

The method of finite elements is certainly, for purposes of discussion, an alternative with practical relevance which has been used with success by many well known authors (/1/, /8/, /15/, /16/, /30/), and always will be. In the modeling of planar MOS transistors the method of finite differences might be given preference because of the simplicity of the region in which the semiconductor equations are to be solved, and on the grounds of mathematical and physical considerations necessary for partioning of this region. A fundamental mathematical preference for one method or the other is certainly not to be given, therefore in the end the choice is philosophical.

A very interesting modification in certain respects complementing the finite differences method was published by Adler /2/, /3/. With the help of this modification much greater flexibility is achieved in the formulation of the finite differences, which can be very attractive.

In the classical method of finite differences the region in which the solution to the differential equation will be sought is subdivided into subregions through a system of lines parallel to the coordinate axes. Further discussion will be restricted to a cartesian coordinate system and a rectangular solution space, which configuration is exclusively found in the work presented here.

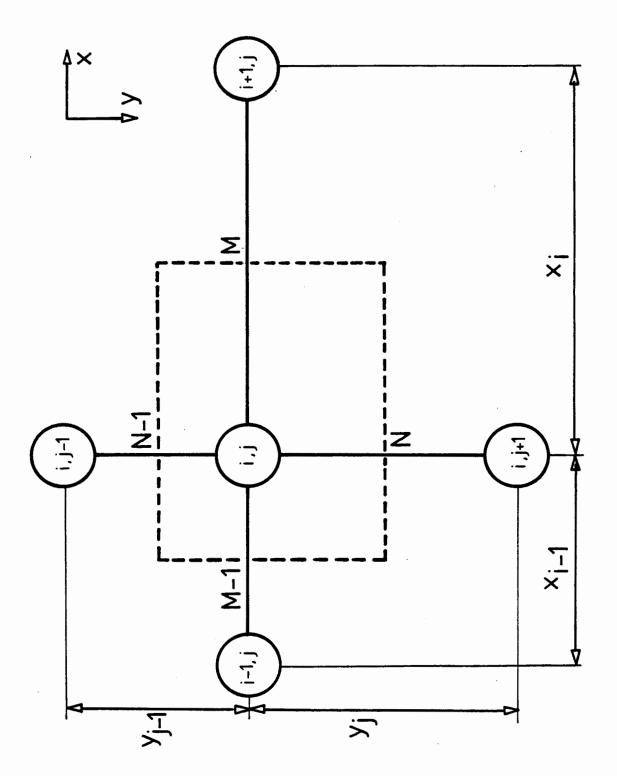

One therefore lays NX vertical (parallel to the y-axis) lines and NY horizontal (parallel to the x-axis) lines through the rectangular region, so one has NX·NY intersection points of these lines, on which an approximate solution for the differential equations is sought. One substitutes only the differential equation on each inner point (i,j) (see figure 3.2-1) through a difference equation, in which the inner point (i,j) - there are exactly (NX-2)·(NY-2) inner points - connected with its four nearest neighboring points (i+1,j), (i,j+1), (i-1,j) and (i,j-1) under the assumption, that the solution of the problem acts as a linear function in the interval spanning these four points and the inner point.

From the already mentioned assumption it becomes clear in an impressive way, how difficult can be the choice for the number of grid lines and their positions for a specific problem. Numerical mathematics has established a considerable amount of evaluation and theories for the purpose of making this choice, e.g. /47/, /140/; in practical cases one needs additionally an enormous amount of experience, in order to advantageously interpret their meaning for a concrete problem.

On the boundary of the region the solution naturally must satisfy the respective boundary conditions, which will be demonstrated later, likewise linear equations can be deduced for the boundary points /47/ - there are exactly 2. (NX+NY-2) points.

Figure 3.2-1: The adopted nomenclature.

The next subsection will deal with the discretization of the quasiharmonic differential equation, a problem upon which a wide spectrum of literature has been published (e.g. in /47/, /49/, /87/, /120/) and as well the linearized Poisson's equation can, as can also the continuity equation, be transformed to this type by a simple method, which will be shown in the following subsection.

#### 3.2.1 The Quasiharmonic Differential Equation

In the (x,y)-plane there exists a finite continuous region G, which is bounded by a piecewise continuous differentiable boundary R. The functions P(x,y), S(x,y) and F(x,y) are continuous in the region G and piecewise continuous on R, the boundary of G. Furthermore P(x,y) is positive and nonvanishing in the complete definition space, likewise S(x,y) and F(x,y) are positive or zero. What is wanted is the function u(x,y) which satisfies the quasiharmonic differential equation:

$$div(P(x,y)\cdot grad(u(x,y))) = S(x,y)\cdot u(x,y) = F(x,y)$$

(3.2-1)

and indeed under the boundary conditions

$$A(x,y) \cdot u(x,y) + B(x,y) \cdot u(x,y)_n = C(x,y)$$

(3.2-2)

with A(x,y), B(x,y) and C(x,y) defined on R, piecewise continuous and positive or zero, likewise A(x,y) + B(x,y) is positive nonvanishing.  $u(x,y)_n$  stands for the externally directed normal derivative of u(x,y) on the boundary R of the region G.

To find the solution to this problem the differential equation will only be integrated in the subregion  $g_{ij}$  around the inner point (i,j). This subregion is the rectangle drawn as a dashed line around the point (i,j) in figure 3.2-1.

$$\iint_{g_{ij}} div(P \cdot grad(u)) \cdot dx \cdot dy = \iint_{g_{ij}} S \cdot u \cdot dx \cdot dy = \iint_{g_{ij}} F \cdot dx \cdot dy$$

(3.2-3)

With the help of a Green's-like theorem the first surface integral in the above expression can be transformed into a line integral over the boundary  $r_{ij}$  of the subregion  $g_{ij}$ .

$$\iint_{g_{ij}} div(P \cdot grad(u)) \cdot dx \cdot dy = \oint_{r_{ij}} (P \cdot (\partial u/\partial x) \cdot dy - P \cdot (\partial u/\partial y) \cdot dx)$$

(3.2-4)

$x_i$  is the geometrical distance between the i<sup>th</sup> and i + 1<sup>th</sup> vertical grid lines and  $y_j$  is the distance between the j<sup>th</sup> and j + 1<sup>th</sup> horizontal grid lines (see figure 3.2-1). Furthermore  $P_N$  stands for the value of the function P(x,y) at the point M, which lies exactly half way between the points (i,j) and (i+1, j), and analogously for  $P_{M-1}$ ,  $P_N$  and  $P_{N-1}$ , which one can best visualize with the help of figure 3.2-1. It follows that:

$$\oint_{\Gamma_{ij}} (P \cdot (\partial u/\partial x) \cdot dy - P \cdot (\partial u/\partial y) \cdot dx) =$$

$$= 0.5 \cdot (y_{j} + y_{j-1}) \cdot (P_{N} \cdot (u_{i+1,j} - u_{i,j}) / x_{i} +$$

$$+ P_{N-1} \cdot (u_{i-1,j} - u_{i,j}) / x_{i-1}) +$$

$$+ 0.5 \cdot (x_{i} + x_{i-1}) \cdot (P_{N} \cdot (u_{i,j+1} - u_{i,j}) / y_{j} +$$

$$+ P_{N-1} \cdot (u_{i,j-1} - u_{i,j}) / y_{j-1}) +$$

$$+ o(x_{i-1} + x_{i}) + o(y_{j-1} + y_{j}) \qquad (3.2-5)$$

The second and third surface integrals of (3.2-3) can, under the assumption that the functions S(x,y) and F(x,y) as well as the solution u(x,y) are smooth in the subregion  $g_{ij}$ , be integrated in an elementary way.

$$\iint_{g_{ij}} s \cdot u \cdot dx \cdot dy = 0.25 \cdot s_{i,j} \cdot u_{i,j} \cdot (x_i + x_{i-1}) \cdot (y_j + y_{j-1})$$

$$\iint_{g_{ij}} r \cdot dx \cdot dy = 0.25 \cdot F_{ij} \cdot (x_i + x_{i-1}) \cdot (y_j + y_{j-1})$$

$$g_{ij} \qquad (3.2-7)$$

One combines (3.2-5), (3.2-6) and (3.2-7) and separates the unknowns, such that one obtains for each inner point (i,j) a linear equation with the following form:

$$\begin{array}{lll} u_{i,j} & \cdot ((y_{j} + y_{j-1}) \cdot (P_{M} / x_{i} + P_{M-1} / x_{i-1}) & + \\ & + & (x_{i} + x_{i-1}) \cdot (P_{N} / y_{j} + P_{N-1} / y_{j-1}) & + \\ & + & 0.5 \cdot s_{i,j} \cdot (x_{i} + x_{i-1}) \cdot (y_{j} + y_{j-1})) & = \\ & = & u_{i+1,j} \cdot ((y_{j} + y_{j-1}) \cdot P_{M} / x_{i}) & + \\ & + & u_{i-1,j} \cdot ((y_{j} + y_{j-1}) \cdot P_{M-1} / x_{i-1}) & + \\ & + & u_{i,j+1} \cdot ((x_{i} + x_{i-1}) \cdot P_{N} / y_{j}) & + \\ & + & u_{i,j-1} \cdot ((x_{i} + x_{i-1}) \cdot P_{N-1} / y_{j-1}) & - \\ & - & 0.5 \cdot P_{i,j} \cdot (x_{i} + x_{i-1}) \cdot (y_{j} + y_{j-1}) & \end{array}$$

No residual term for the estimation of the error is provided in (3.2-8). With a nonequidistant grid  $(x_i \neq x_{i-1}, y_j \neq y_{j-1})$  the error, in the first approximation, is reduced linearly with the line spacing. An exact formulation of the estimated error must be made, however, such a formulation is not a central point of this work but can be found in the relevant literature /47/, /120/.

The discretization of the boundary points presents no problem. It has been carried out in great detail in countless textbooks on numerical mathematics (e.g. /47/), therefore it is refrained from a simple repetition.

One combines the equations for all of the grid points, which are linear without exception, in one system, such that this system can be presented in matrix form.

$A \cdot u = b$

In the above equation u represents a vector of length NX NY, in which all of the desired  $\mathbf{u_{i,j}}$  are included. b is the pertinent vector for the right hand side. The matrix A in many practical cases is of very high rank NX NY. As the coefficient matrix of the system equations it has a maximum of five non zero elements in each row. The numerical solution of a system of sparsely linear equations of this type will be dealt with in section 3.3.

# 3.2.2 Poisson's Equation

The linearized form of Poisson's equation (3.1-3) is tailor made for the quasiharmonic equation whose theory was sketched in the last subsection. In order to see this established in its entirety, it is necessary to clarify the boundary conditions of Poisson's equation as well as the structure of the equation to be solved, and also the appropriate boundary conditions are necessary in order to consider and thereby classify the problem clearly and place it in proper perspective.

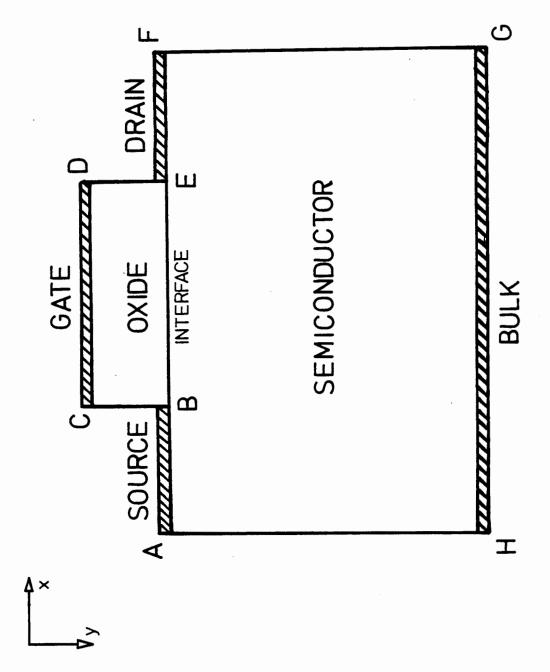

Figure 3.2-2 shows the geometry which was used in the simulation. Inside the rectangular region A-F-G-H, which represents the silicon, the system of semiconductor equations must be solved, in the region C-D-E-B which represents the gate oxide, only Laplace's equation must be solved.

The following concrete considerations apply only to Poisson's equation. The contacts (AB: Source, EF: Drain, GH: Bulk) will be assumed to be ohmic. The potential will hereafter have the value of the applied potential plus the built in potential due to the doping. On the vertical edges of the semiconductor (AH, FG) the normal derivative of the potential, that is, the lateral electric field component, must go to zero. This consideration is naturally justified when the vertical edges are far enough away from the channel. On the interface (line BE) equation (3.2-9) must satisfy Gauss's law.

Figure 3.2-2: The simulation geometry.

$$c_{ox} \cdot (\partial \psi / \partial y)_{ox} = c_{si} \cdot (\partial \psi / \partial y)_{si}$$

(3.2-9)

In the oxide a solution is to be found for Laplace's equation which is coupled to Poisson's equation in the semiconductor, consequently (3.2-9) represents the boundary condition which must be satisfied along the interface. On the vertical edges of the oxide (CB,DE) the normal derivative of the potential must again go to zero, and on the gate contact (CD) the potential will be set equal to the applied voltage minus the flat band voltage.

The eventual existence of slow interface states  $N_{\rm SS}$  will be taken into account in the flat band voltage. Gauss's law permits a physically consistent consideration of the accumulation of charge by the slow interface states /126/. Due to the decreased importance of these interface states in modern transistors, the added expense of this alternative is not justified.

With the above defined boundary conditions it is easy to verify that the linearized form of Poisson's equation is a special case of the boundary value problem dealt with in 3.2.1. Only the following substitutions need to be made:

```

u(x,y) \dots \phi(x,y)

P(x,y) ... 1

S(x,y) \dots n(x,y) + p(x,y)

(n(x,y)) and p(x,y) contain only the known values

of \psi^k and \varphi_{\underline{a}}^k)

F(x,y) ... n(x,y) - p(x,y) - C(x,y) - div grad <math>\phi^k

For the boundary one has:

in the cases of the contacts

A(x,y) = 1

C(x,y) = const

(applied plus built-in potential)

B(x,y) = 0

in the cases of the vertical boundaries

A(x,y) = 0

B(x,y) = 1

C(x,y) = 0

```

in the case of the interface:

$$A(x,y) = 0$$

$$B(x,y) = \varepsilon_{si}$$

$$C(x,y) = \epsilon_{ox} \cdot (\partial \phi / \partial y)_{ox}$$

Laplace's equation in the oxide is only a trivial case of Poisson's equation and will not be given further consideration here.

The discrete form of Poisson's equation can, with the help of the substitution presented in (3.2-8), be determined in an elementary way, by way of a direct copy of (3.2-8) with a partial change of notation.

# 3.2.3 The Continuity Equation

At first glance the continuity equation does not fit the theory of the quasiharmonic differential equation. First by the transformation of variables

$$\mathbf{s} = \mathbf{e}^{-\frac{1}{2}}\mathbf{n} \tag{3.2-10}$$

the required analogy will become evident. The continuity equation has the following form:

$$div(\mu_n^*e^{\phi} \cdot grad s) - s \cdot e^{\phi p}/(\tau_p^* \cdot (n+1) + \tau_n^* \cdot (p+1)) = = -1/(\tau_p^* \cdot (n+1) + \tau_n^* \cdot (p+1))$$

(3.2-11)

The linearization of the denominators of the recombination terms is not necessary here, in the case of MOS transistors, because on the one hand this term makes no combribution to the basic carrier transport, but serves only to avoid physically unrealistic carrier depletion in the drain/substrate diode (see chapter 2) and on the other hand, through the use of an iterative solution procedure for the differential equation (see section 3.3) a first order linearization occurs automatically.

The boundary conditions are simple as was the case for Poisson's equation. The contacts (AB, EF and GH in figure 3.2.2) are taken as ohmic,

and the carrier concentrations are equal to their equilibrium values. On the remaining boundaries (BE, FG and AH) no normal current components may exist at any time.

The reader can easily see, by way of the above considerations, that the continuity equation fits into the scheme of boundary value problems dealt with in section 3.2.1, such that further discussion in this direction can be dispensed with.

The above presented derivation may indeed work very satisfactorily and completely, but still there are several additional tricks to be applied, without which the transformation of this theory into a computer program would surely be condemned to failure.

The first problem that exists is to choose a suitable interpolation of the function in (3.2-12):

$$P(x,y) = \mu_{n} \cdot e^{\frac{1}{2}}$$

(3.2-12)

The mobility is indeed, in general, a function with a small variation, such that it can be linearly interpolated between neighboring grid points. The exponential function of the potential surely cannot be interpolated in the same way. A simple method is the geometrical averaging of the function, which agrees with a linear behavior of the potential. An error analysis of this method has been carried out by Jesshope /66/, /67/. This interpolation will not be exact even when the potential difference between two adjacent points is small. A satisfactory interpolation algorithm was first published by Scharfetter and Gummel /110/. That algorithm was in essence based upon physical considerations; its mathematical consistency was verified by Barnes /7/. It holds that for the interpolation between the points (i,j) and (i + 1, j):

$$e^{\psi}_{H} = e^{\psi i, j \cdot (\psi_{i, j} - \psi_{i+1, j}) / (e^{\psi i, j} - \psi_{i+1, j} - 1)}$$

$$= e^{\psi i, j \cdot ber(\psi_{i, j} - \psi_{i+1, j})}$$

(3.2-13)

with:  $ber(x) = x/(e^{x} - 1)$  (The Bernoulli function).

Special attention must be paid to the programming of the Bernoulli function in order to avoid overflow or underflow of the numerical range of the computer /60/. A fortuitous secondary effect of using this interpolation is, that, when one divides the therewith obtained difference equation by  $e^{\psi i,j}$ , which causes absolutely no problem, only exponential functions of potential differences appear in the coefficients, which decisively increases the numerical stability of the system of equations.

A further point which requires close attention for the solution of the discretized continuity equation is the extremely large interval for S, (3.2-10) which has been obtained by substitution of a new independent variable. It is finally necessary to reduce the solution interval with the help of a similarity transformation. A physically based scaling rests upon the use of  $e^{\phi}$  as the transformation variable /117/. From this method one obtains as independent variable the carrier concentration, whose dynamic range can indeed be very large but presents no difficulty for modern computers. An unfortunate side effect of this similarity transformation is that the symmetry of the coefficient matrix is lost. The global condition number of the system of equations will not be changed through the similarity transformation /39/.

An interesting alternative to the discretization of the continuity equation which was sketched here is to mention the connection with the "stream function" method which was first published by Mock /90/. The stream function method was not tested in this work, the method presented above functioned satisfactorily. The method of "stream functions" enjoys great popularity especially with the Japanese authors /69/, /131/. An evaluation of this method on purely theoretical considerations is very problematic and therefore will not be attempted here.

## 3.2.4 The Grid Generation

Careful attention must be given to the selection of the grid points in order to sufficiently bound the discretization error, which has a very strong influence upon the convergence characteristics of the equations and therewith upon the complete system.

Chapter 3.2

It is impossible to choose an equidistant grid, because the spacing must be compatible with the dominant region of greatest numerical difficulty. Consequently, the use of an equidistant grid would result in too many unnecessary points in other regions. Therefore an enormously large number of required grid points would result, which would cause noticeably undesirable memory and computation time requirements. A further, more severe disadvantage also exists. In a region in which a solution variable is almost constant, small spacings can result in numerical instabilities which can be traced to the round off error which results from taking the difference between two nearly equal numbers.

Because of the above mentioned reasons, a grid with unequal spacing must be used, which will then be checked for accuracy in a special phase of the solution (see appendix C). It will then, if necessary, be adapted where the most recently obtained behavior of the variable will be used as the new basis for the calculation.

The underlying conditions for the grid generation can be divided into two different groups: there is fundamentally, on the one hand, the spacings in regard to these conditions, which are to be fulfilled under all circumstances, and on the other hand the conditions are considered on the grounds of doping profile, electrostatic potential and carrier distribution, so far as these last conditions do not conflict with the first group. It should possibly be mentioned here that the grid generations in the x and y directions are independent and therefore no conditions exist in this regard.

Requirements which take absolute priority are that there exists a minimum value for the spacing and that the ratio of successive spacings must be between certain minimum and maximum values, whereby the maximum allowable progression of the grid is established.

The considerations with respect to the doping profiles exist as criteria relative to the active doping concentration between two successive grid points, which is only important when at least one of the two doping levels is greater than some minimum value.

Respectively the electrostatic potential must satisfy the requirement that the absolute potential difference between two adjacent grid points may not exceed some maximum value.

A requirement imposed by the charge carrier concentration is that the ratio of the electron density (or the hole density for p-channels) between two adjacent points must lie between certain minimum and maximum values.

The setting of the bounds for each of the above requirements by strong mathematical considerations is highly unrealistic, because some remainder may arise which can only be evaluated by an enormous, unjustified expense. The values of the bounds which were actually used came from intuitive or physical considerations and were proven plausible by many test cases. The criteria were placed in a separate part of the program in a modular fashion such that changes could be easily made.

#### 3.3 The Solution of the Discretized Fundamental Equations

Given the system of equations

$A \cdot u = b$

with the property that the coefficient matrix A is derived from a five point discretization using finite differences. In general the rank of this matrix is very large (typically 2000-3000) and furthermore there are only a maximum of five elements in each row and column which are not equal to zero. Consequently, the matrix is very sparsely filled, it is sparse. Because of the discertization of Poisson's equation the resulting matrix is symmetrical and positive definite. In principle these properties also hold for the coefficient matrix of the continuity equation, whereby it should be noted, that these properties are lost through an eventually required similarity transformation. Further properties of these matrices will not be required for the following discussion, therefore, the relevant literature can be referenced /87/, /139/, and /140/.

Two kinds of approaches can be used for the solution of these types of linear systems of equations: direct and iterative approaches. The classical direct method, Gaussian elimination, does not take into account the sparseness and the special structure of the coefficient matrix, such that the required computational effort (rank (A)<sup>3</sup>) is in general, not acceptable. However, there exists a remarkable number of modified Gaussian elimination methods /43/, which consider to some extent the above mentioned properties of the coefficient matrix. Because the solution of the system of equations is embedded in an iteration procedure, it therefore very often must occur that priority has to be given to the iterative methods for the solution of the system of equations. This holds even more as through the iteration procedure very good initial guesses are available /42/.

In the scope of this work a large number of iterative solution procedures were programmed and tested. The relaxation processes (SOR, LSOR, SSOR, S2LOR) were ruled out in the first test comparison because of their slow rates of convergence. The programming of these methods is indeed very easy and there

Chapter 3.3

exists a wide spectrum of literature /122/, /139/, and /140/ in which their convergence characteristics and their mathematical foundations are exactly analysed, such that the attraction of these methods is that they are very serviceable. After careful consideration the choices were limited to the ADI method /122/, the AFP method /44/ and the SIP method of Stone /123/. Careful comparison of these three methods indicated an unmistakable advantage for the SIP methods, as was also confirmed in /105/.

The basic idea of Stone's method is that a special matrix N is added to the coefficient matrix A, such that the resultant matrix (A + N) can be decomposed trivially into the product of an upper triangular matrix and a lower triangular matrix.

$$(A + N) \cdot u = (L \cdot U) \cdot u$$

Under this condition the construction of an iterative process is simple. It holds namely:

$$(A + N) \cdot u = (A + N) \cdot u = (b - A \cdot u)$$

hence one can obtain:

$$(A + N) \cdot u^{k+1} = (A + N) \cdot u^k + (b - A \cdot u^k)$$

Because the right side of this system of equations is known and because (A + N) is simply factorizable, the above equation represents an extremely efficient iteration scheme. Furthermore, if the norm of N is very much smaller than the norm of A, a fast convergence rate can be intuitively expected.

Stone further gave a simple, and constructive possibility for the choice of the matrix N; closer examination regarding this topic would greatly expand the scope of the present work, therefore those interested are referred to the original work /123/ or the explanations of this procedure in /49/ and /120/.

An eventual disadvantage of this method is the fact, that the vectorization of this algorithm in view of a computer with pipeline architecture, as is also noted in /42/, and the efficient use of fundamental modular programs of linear algebra /77/ are not simple.

## 4. Typical Applications Examples

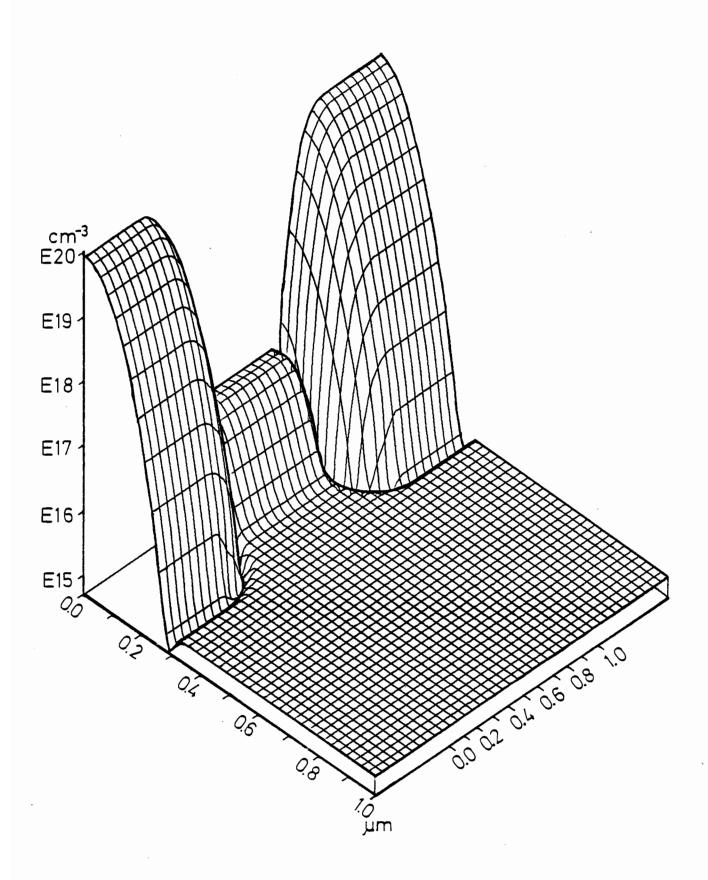

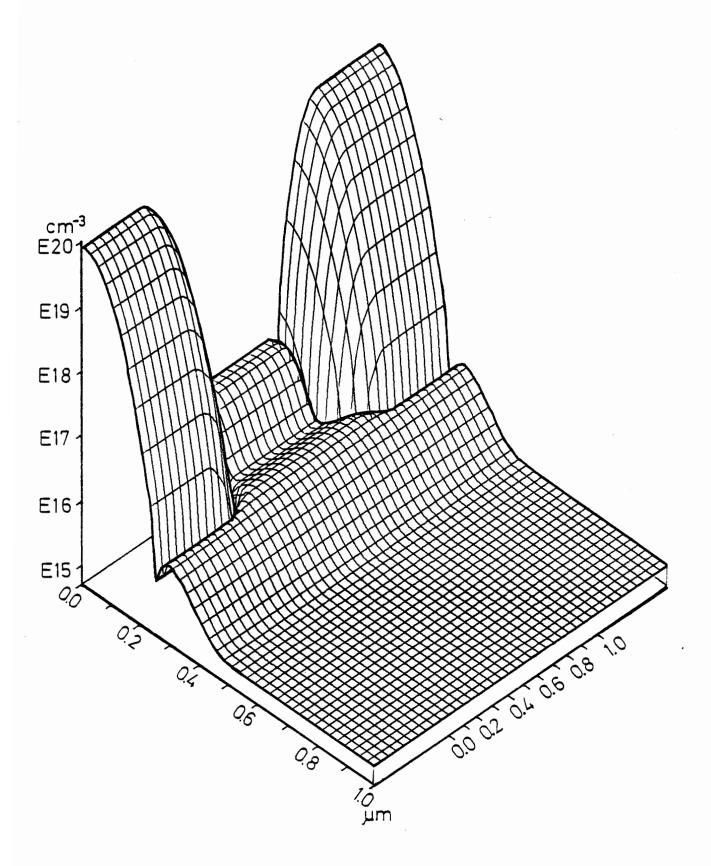

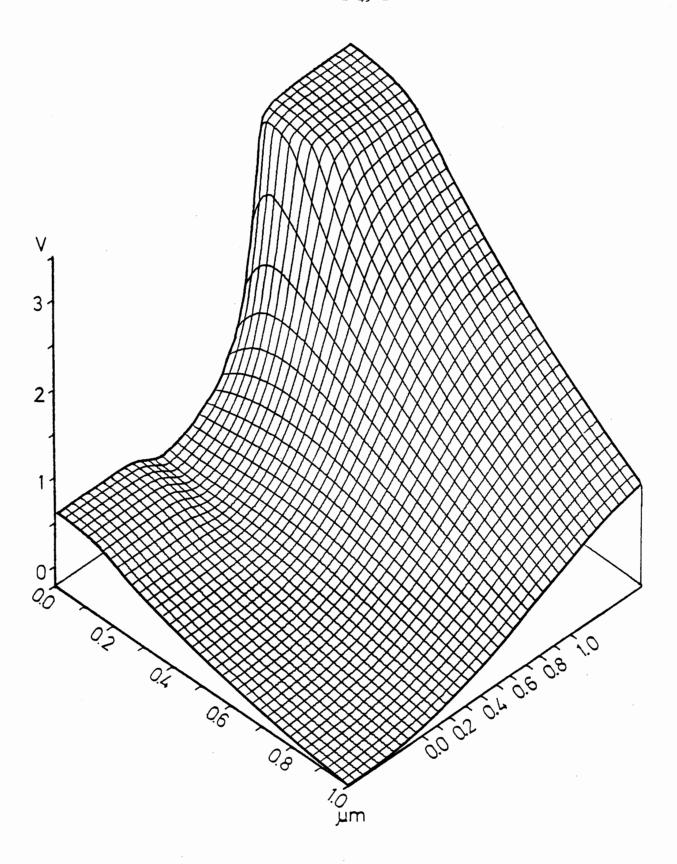

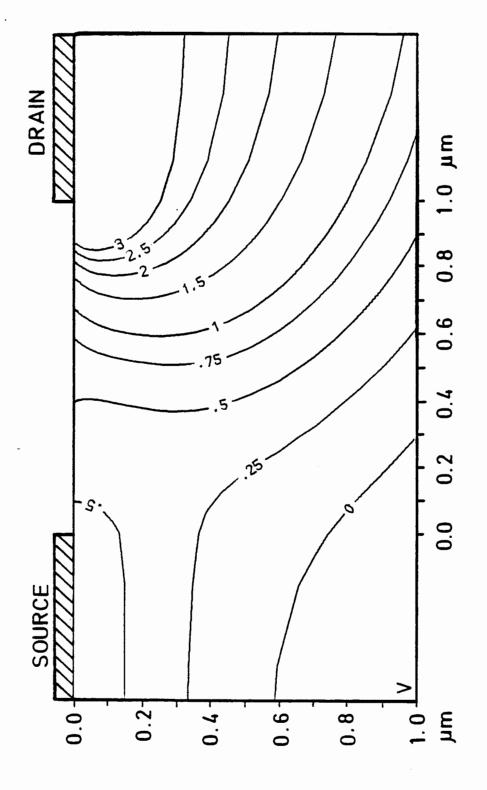

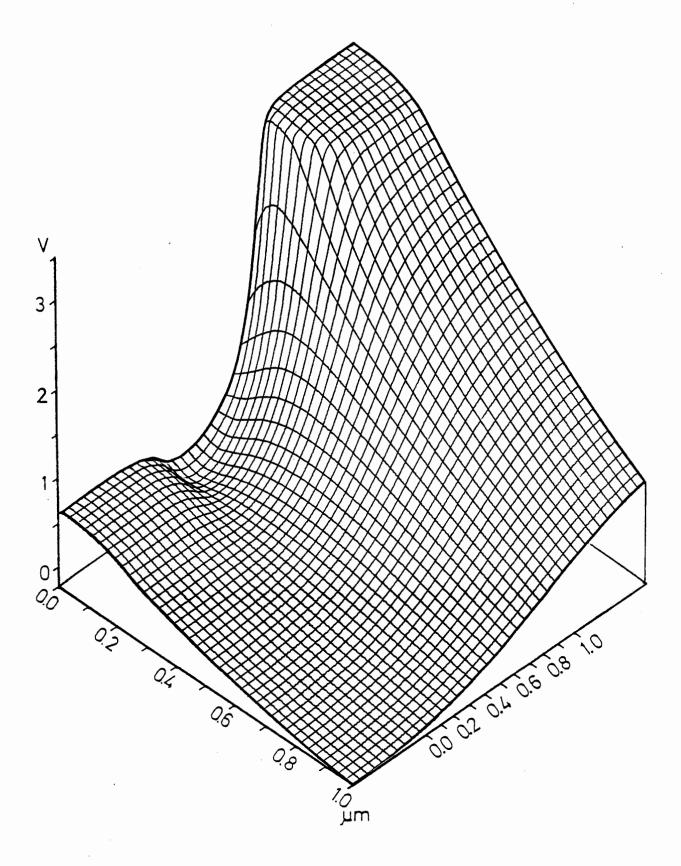

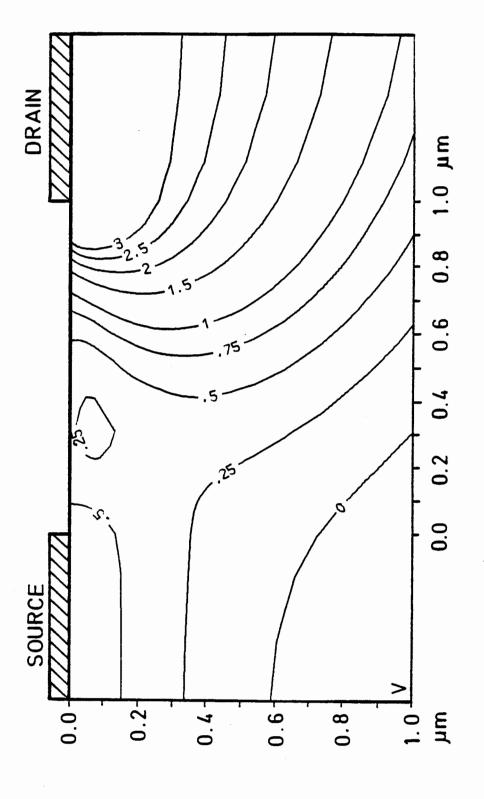

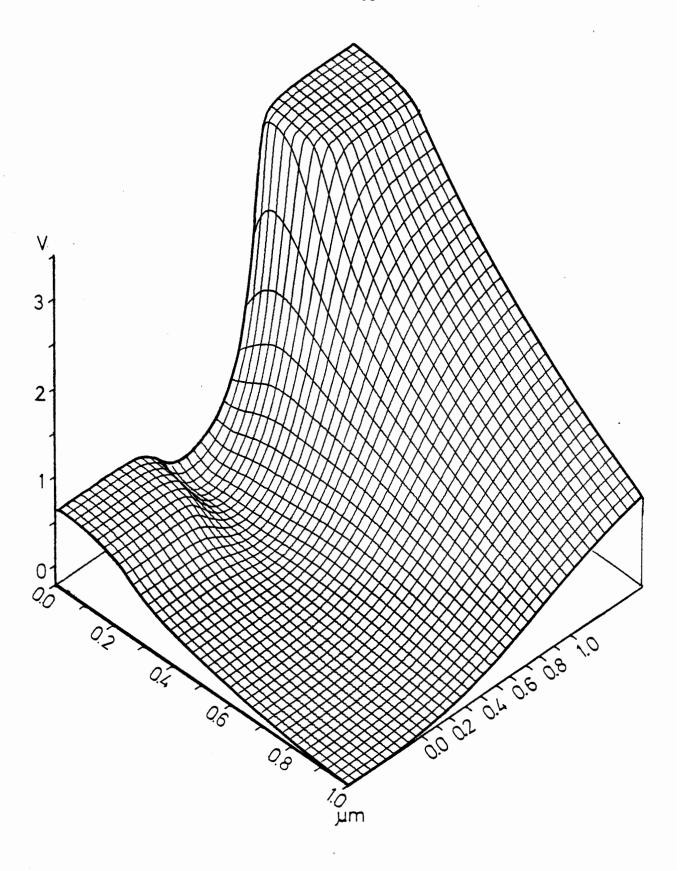

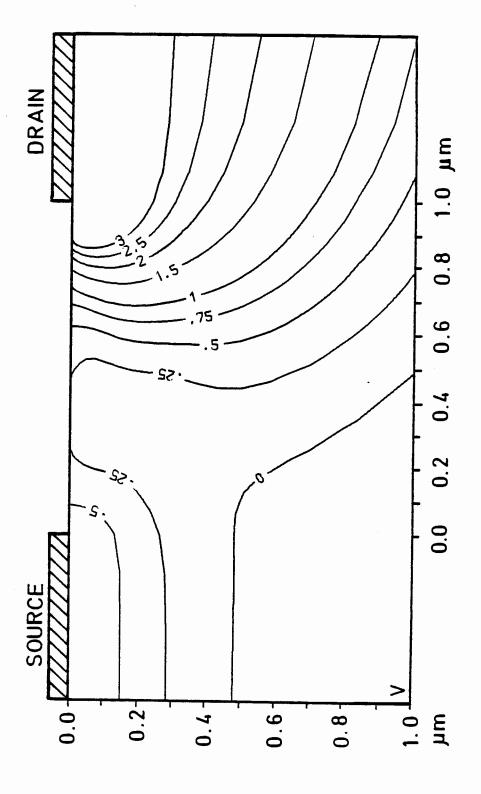

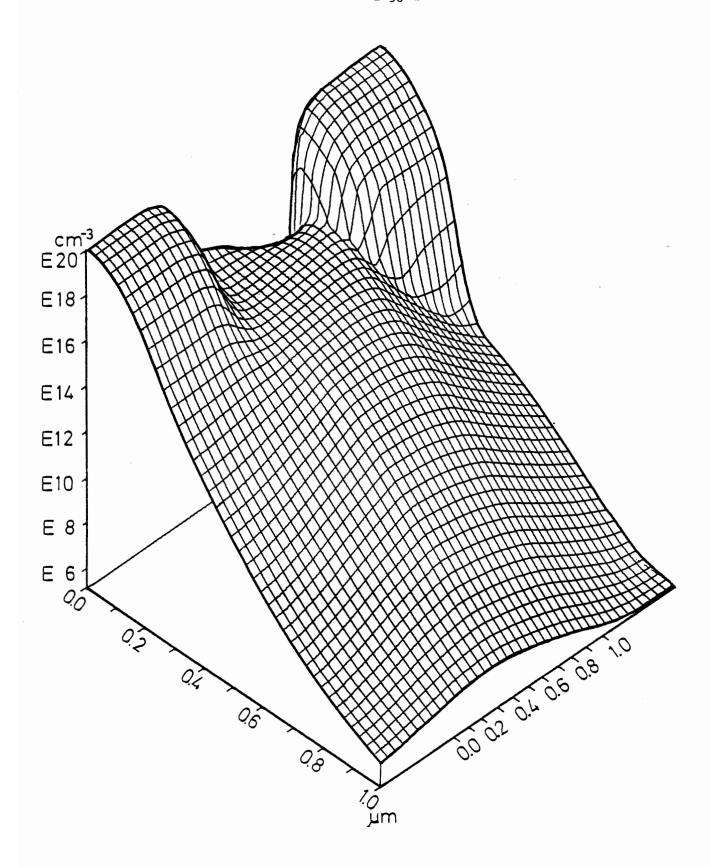

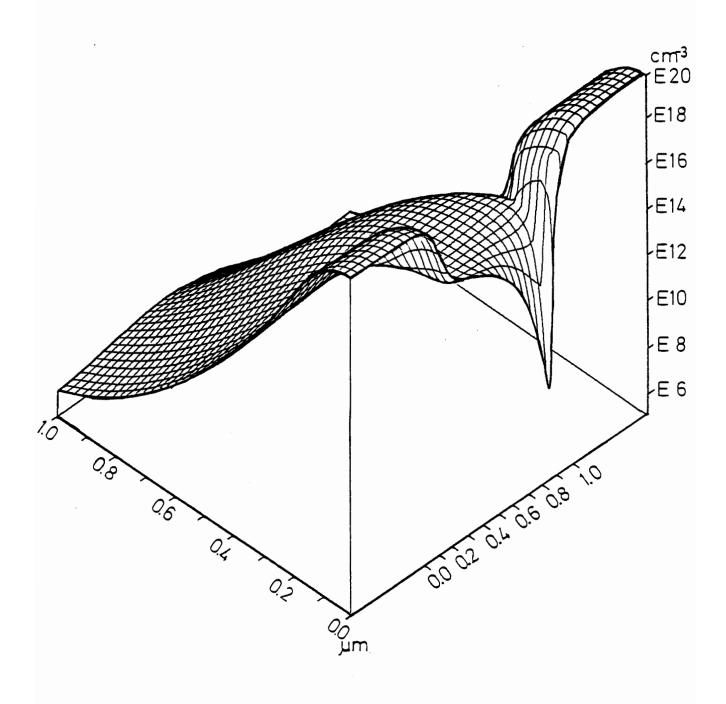

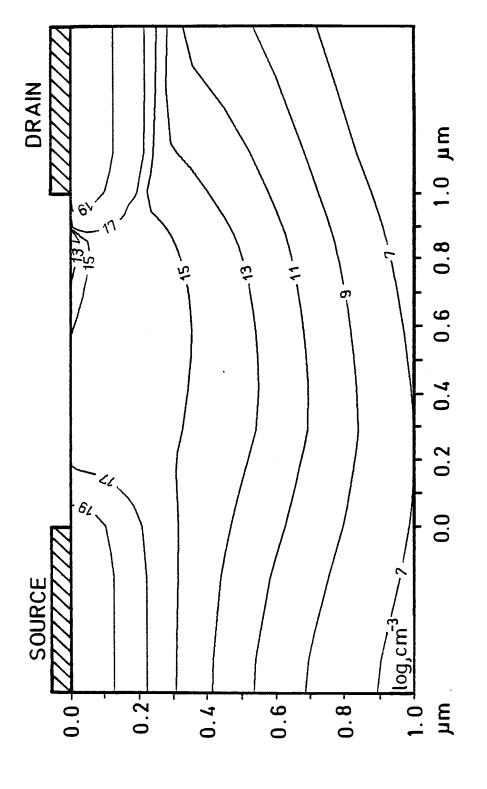

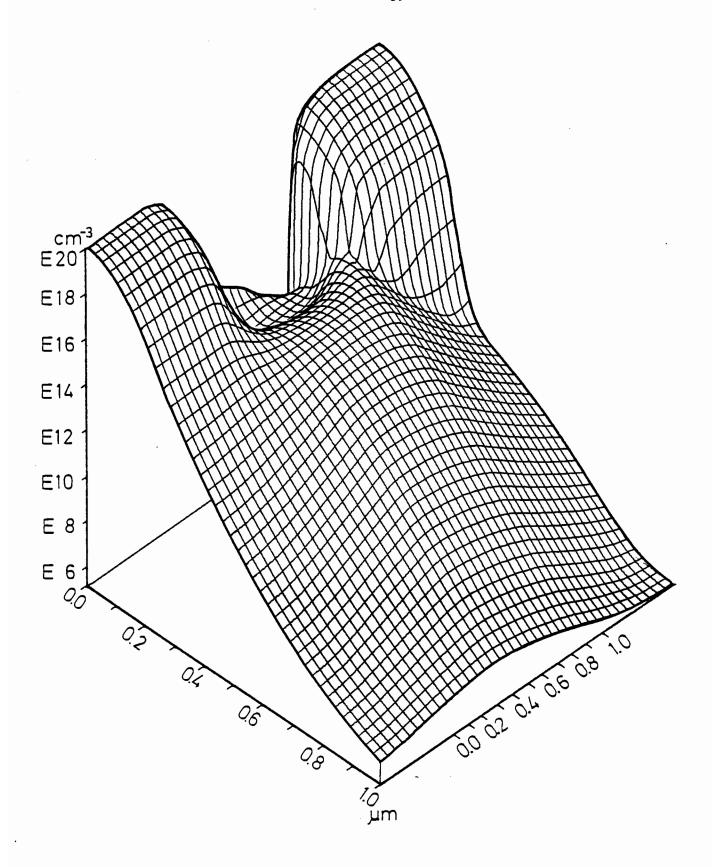

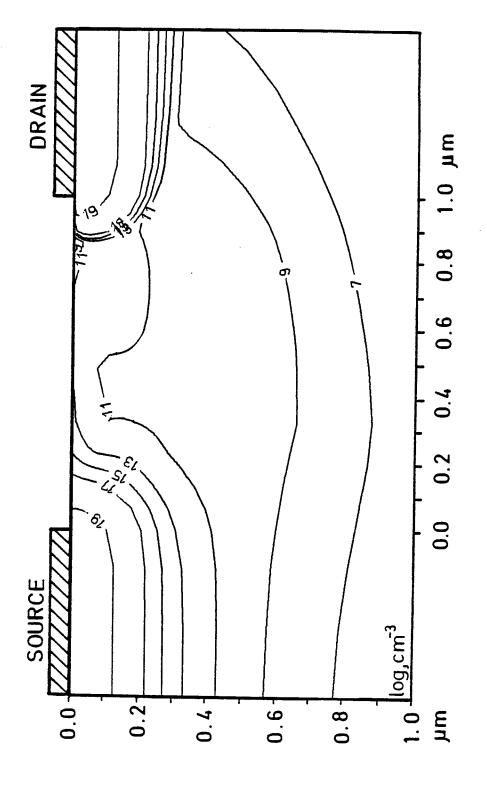

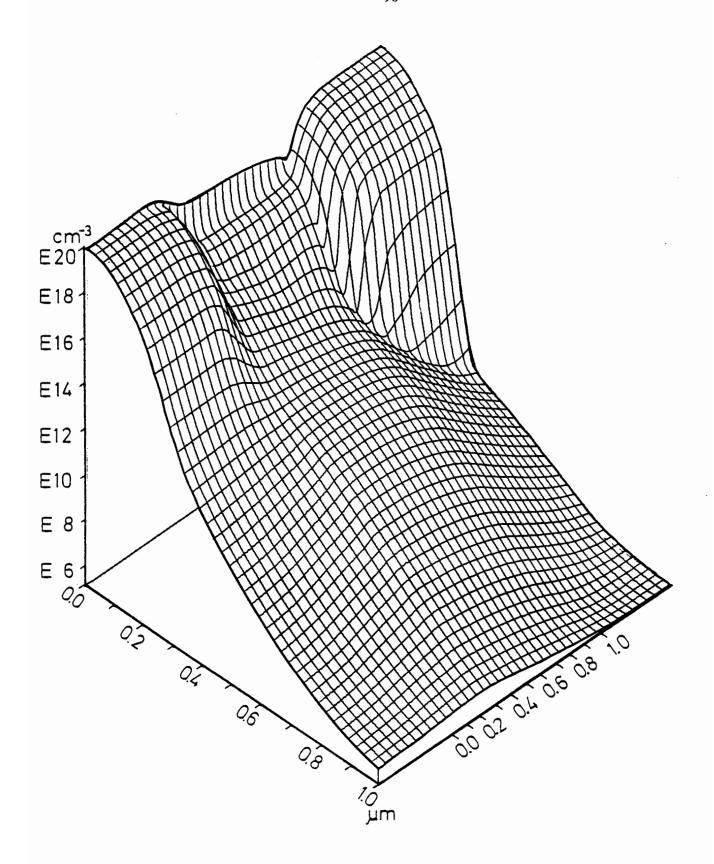

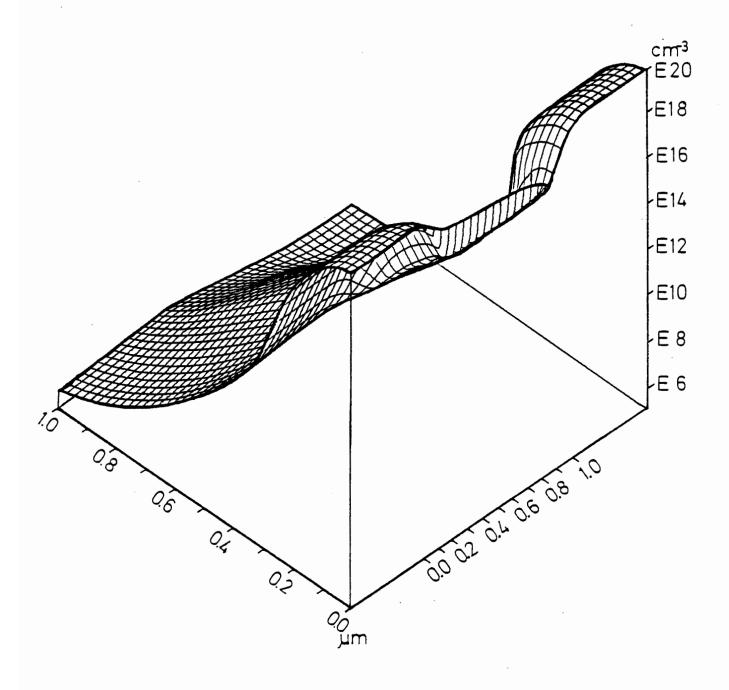

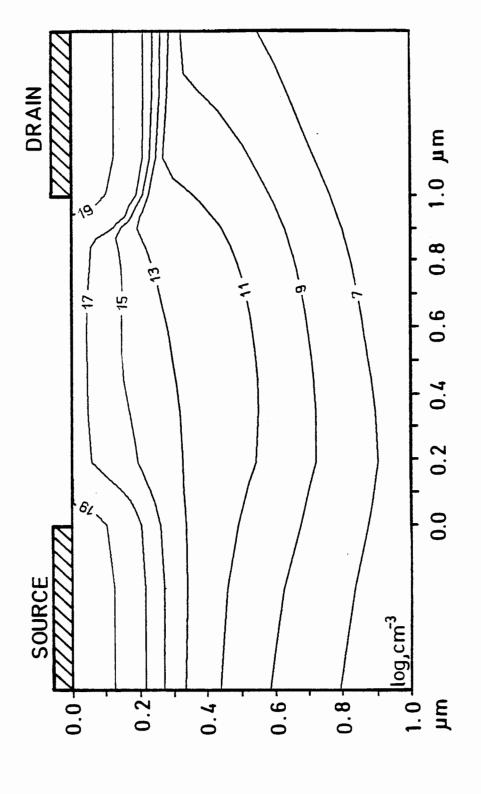

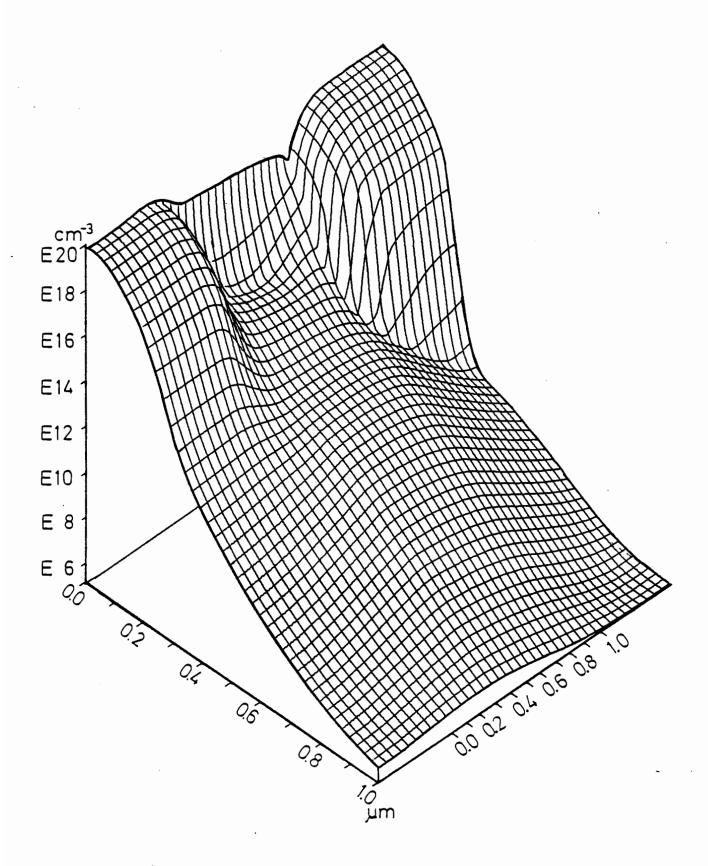

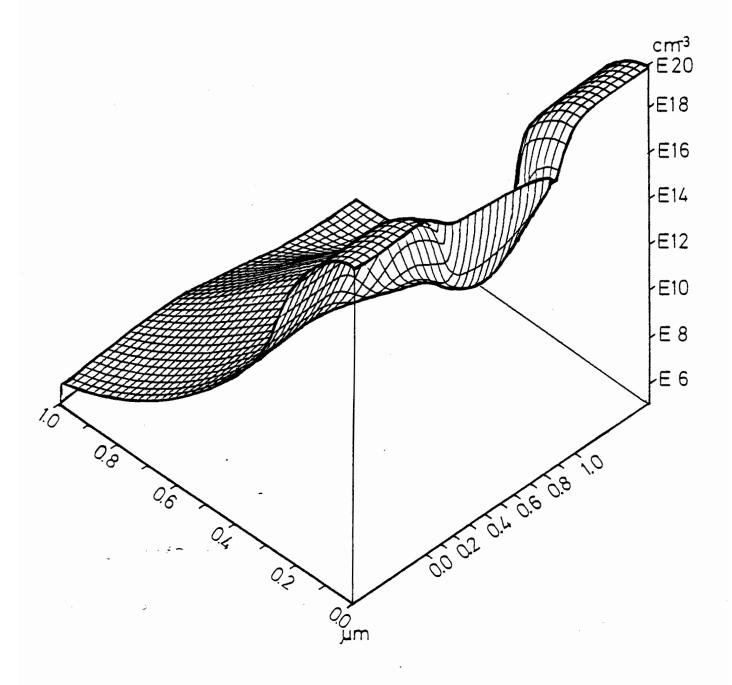

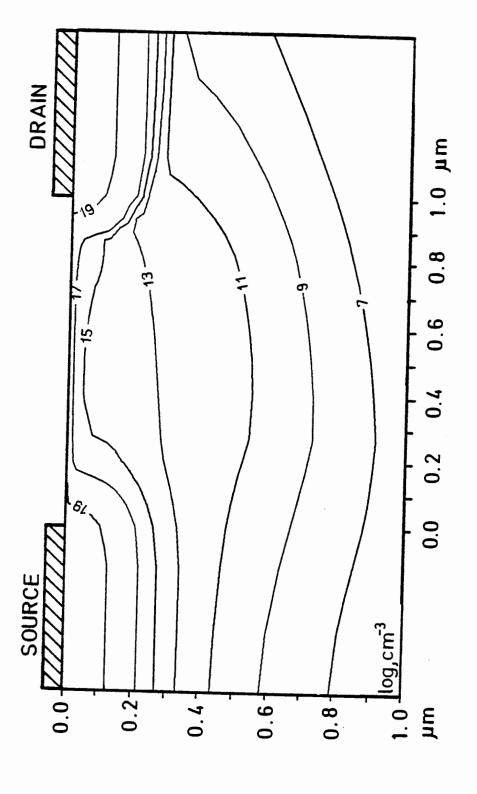

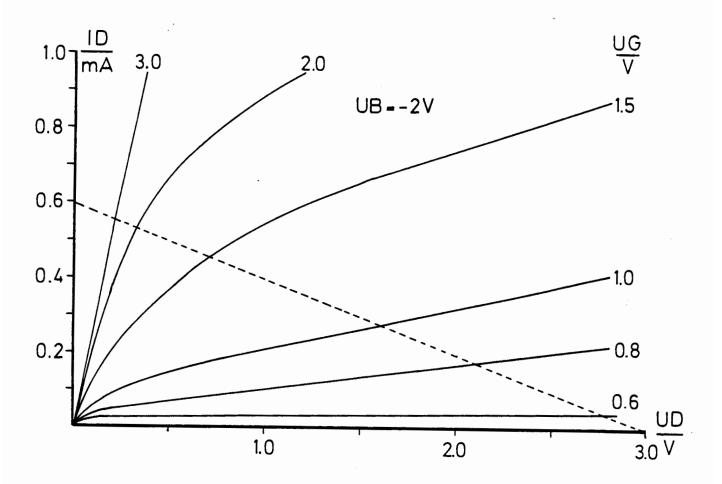

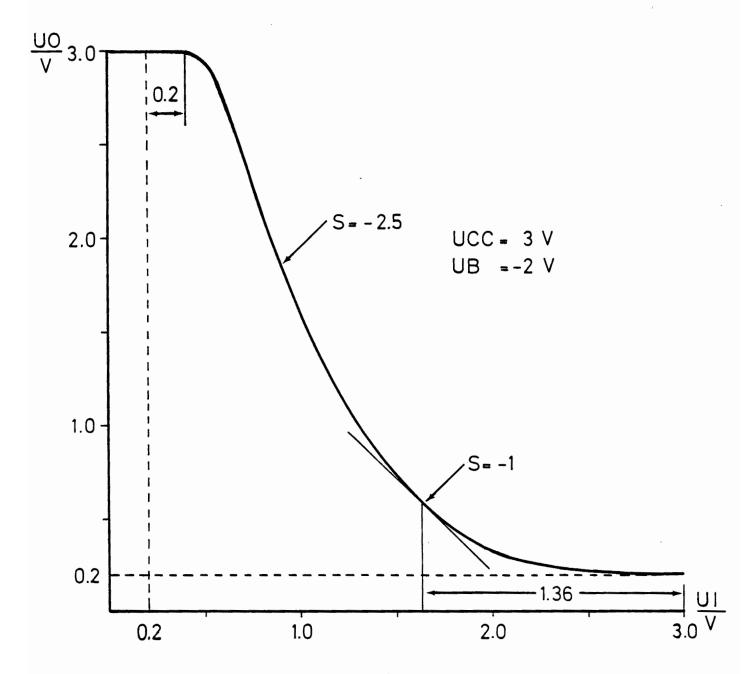

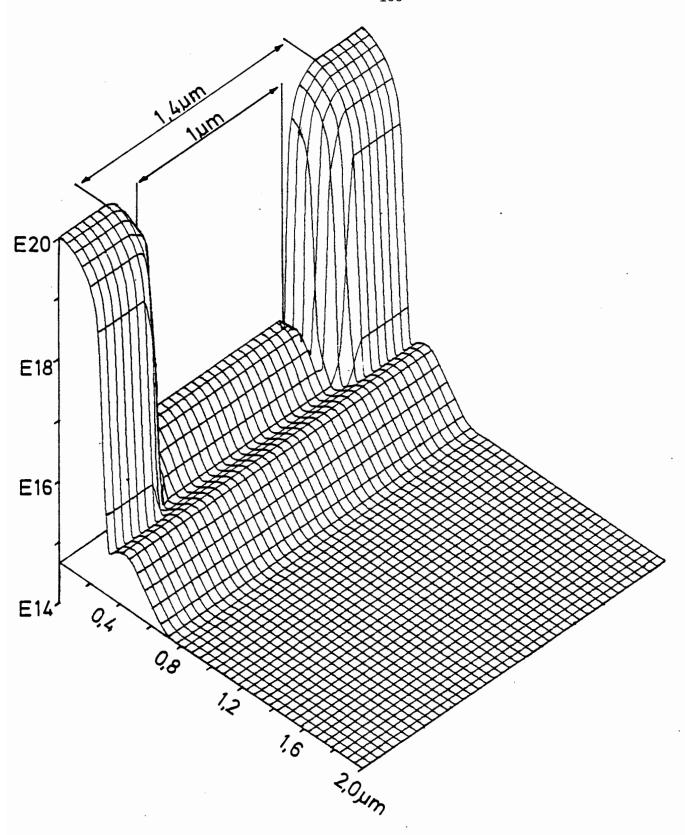

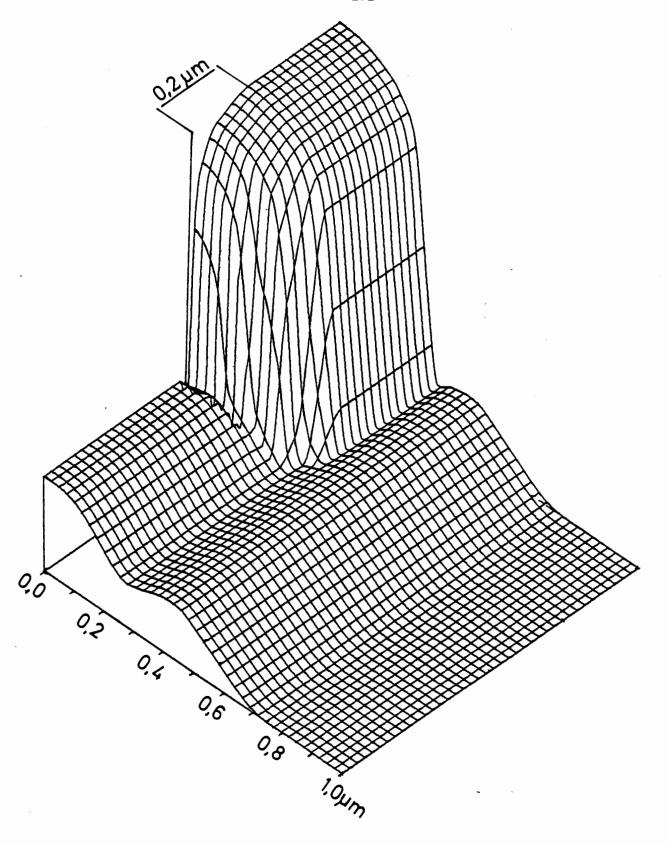

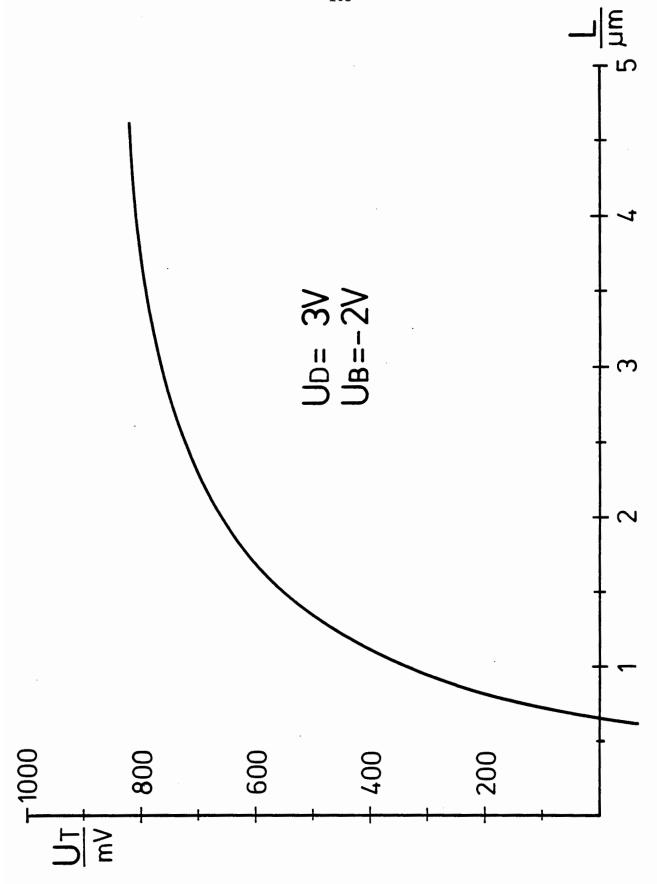

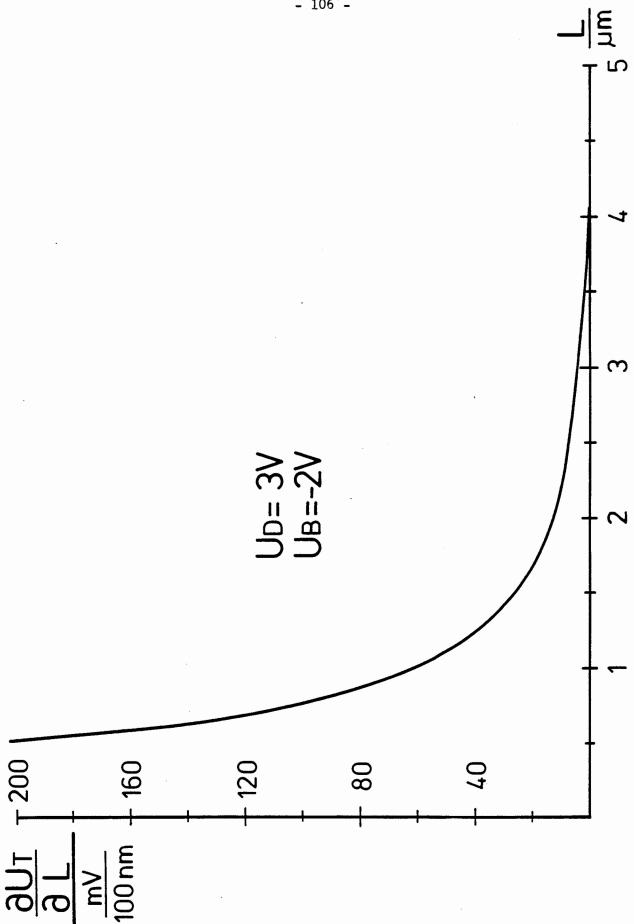

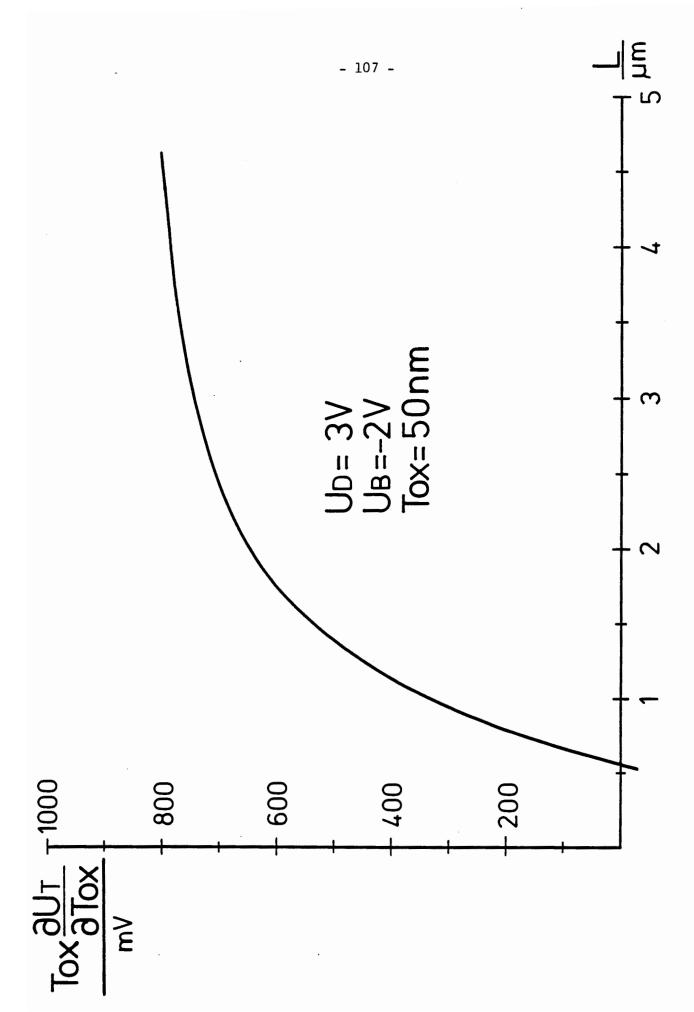

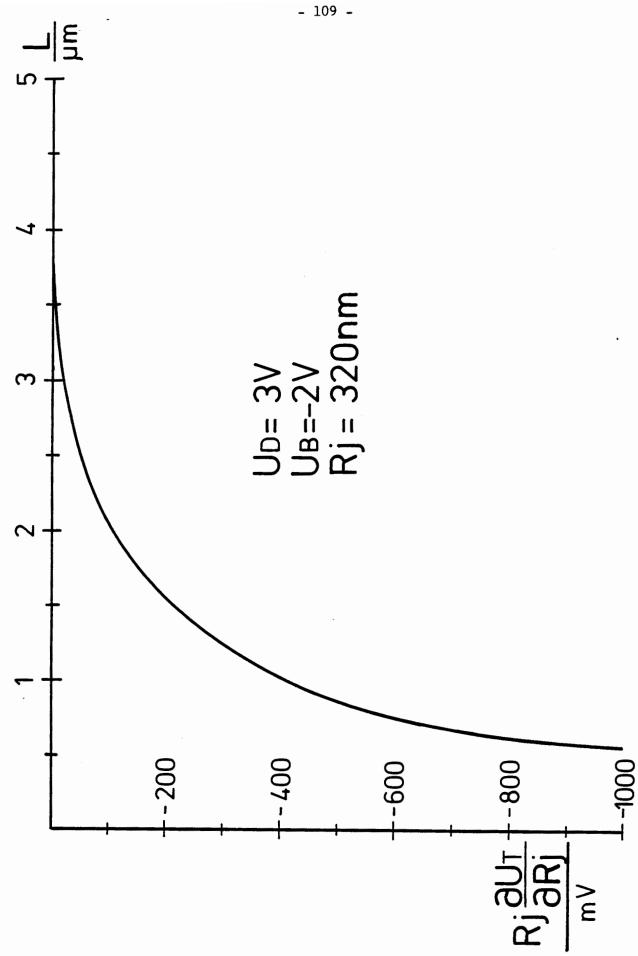

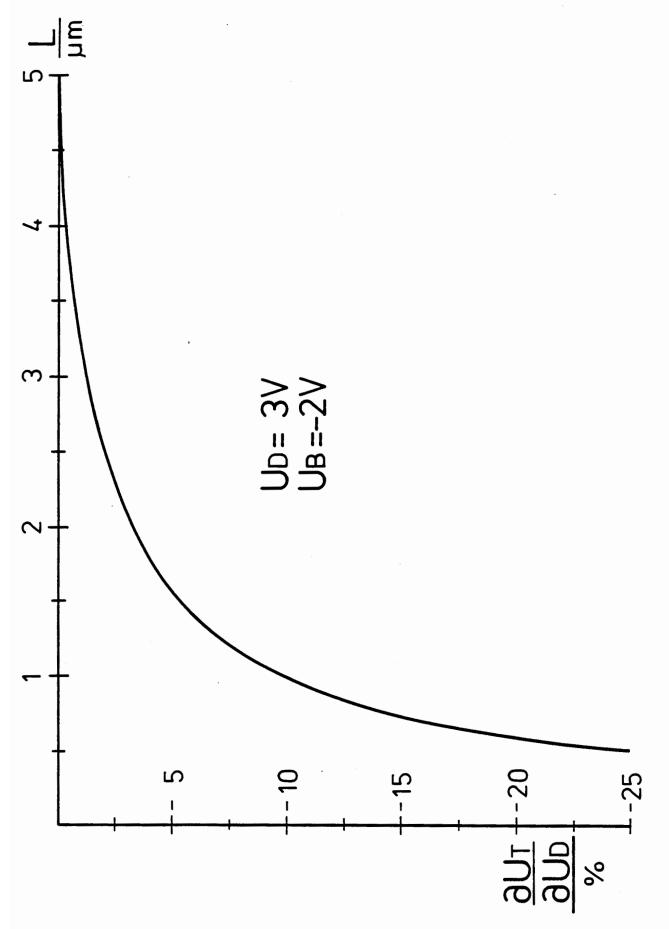

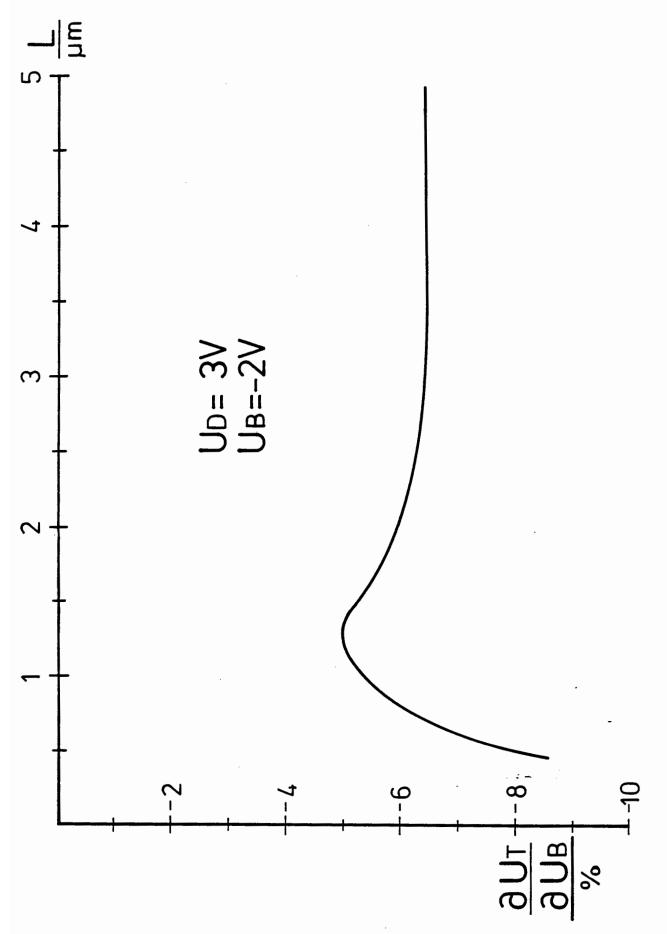

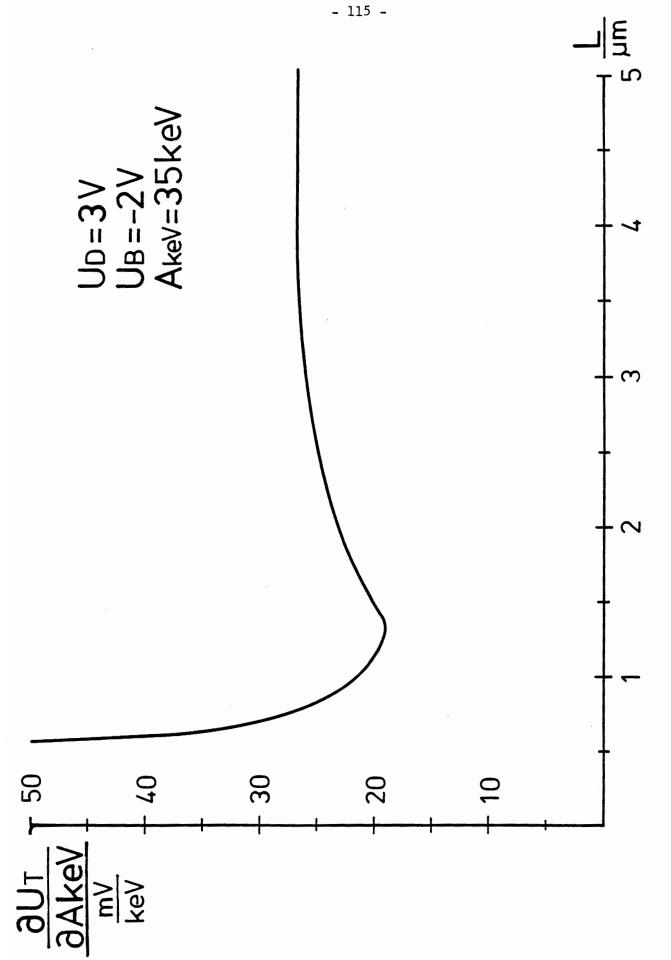

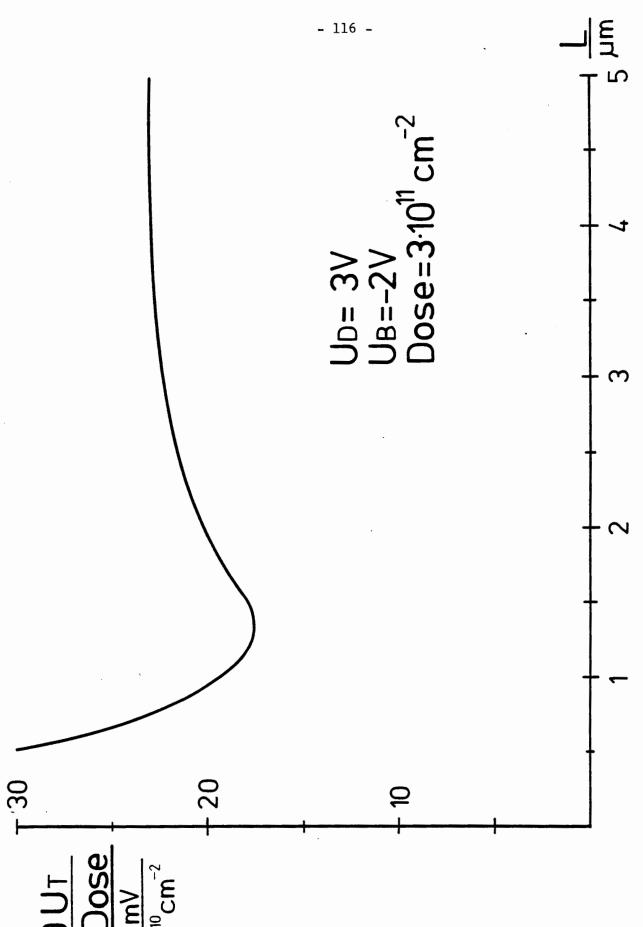

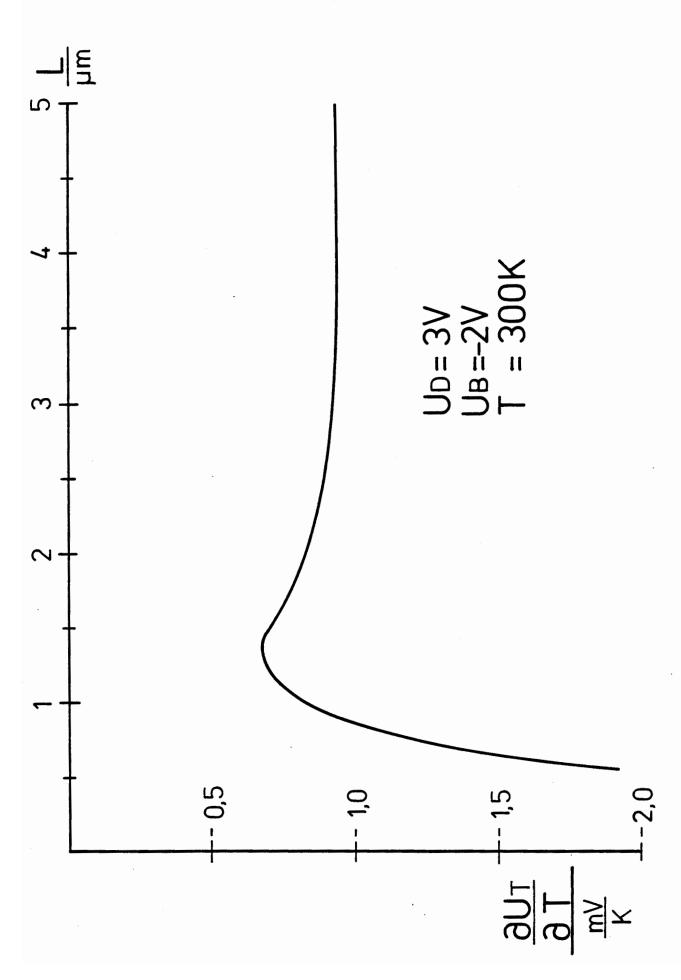

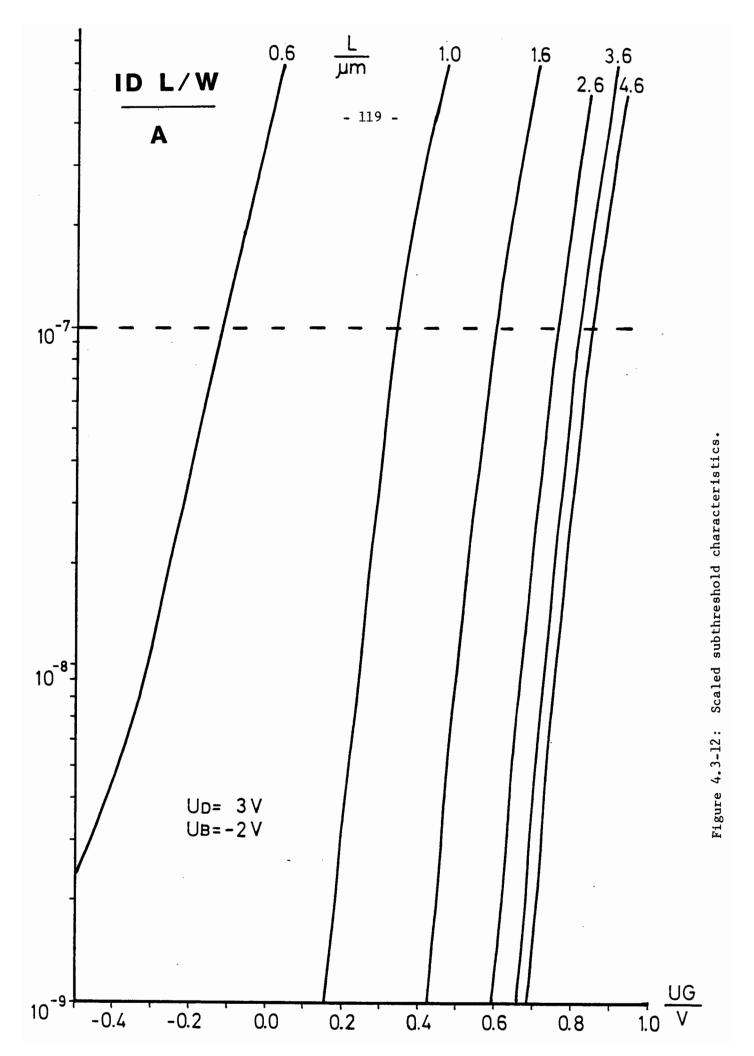

The demonstration of a finished work by typical examples is unquestionably one of the most important points of the work itself. Examples first bring life to abstract formulas; they stimulate the imagination, induce ideas and thereby often times build a graphic basis for further and analogous works. The appropriate choice of such examples can be very difficult when many such possibilities exist, one must appeal to a wide spread public yet only a small space is available.